”芯片验证-UVM“ 的搜索结果

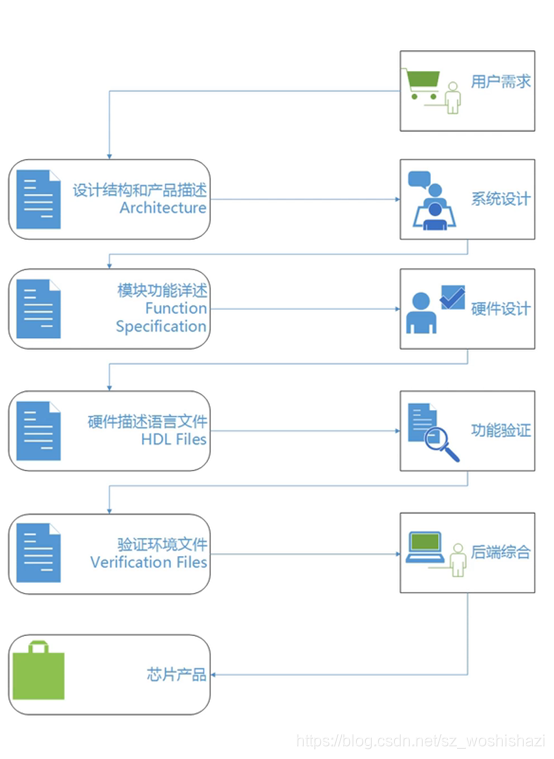

UVM验证方法学 ASIC验证分解 验证策略和任务的分解 AMBA可重用、灵活性、兼容性、广泛支持 一.验证的Roadmap 1.ASIC芯片项目流程 市场需求>产品定义>硬件、软件>芯片测试>产品发布 硬件:芯片定义>...

芯片数字验证及数字设计常见面试问题

标签: uvm

文档包含芯片数字验证及数字设计常见面试问题,可以作为自己平时看资料的补充,看一下那些是之前漏掉了没有关注到的。

新人怎么学习ic验证,芯片验证怎么学习入门!

verdiverdi [ 选项 ] [ 文件 ]-f [文件名]: 在某文件中索引工程包含的文件路径;-top [名称]: 工程名称,后接的是tb文件的 Module 名字;-nologo: 无欢迎界面;-ssf [文件名].fsdb: 指定已有的波形文件。

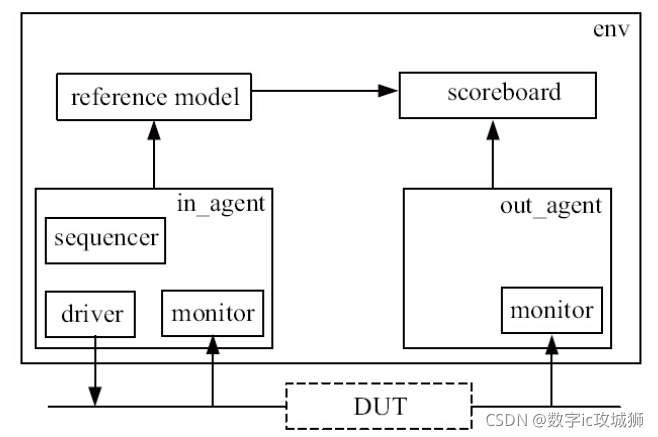

随着集成电路规模和复杂度的提高,其验证工作也日益复杂和重要,验证周期己经达到甚至超过整个芯片设计周期的70%,因此,急需找到一种高效的验证方法,以便提高验证效率,增强验证平台的可重用性。基于SystemVerilog...

1.简述 UVM 的工厂机制 Factory 机制也叫工厂机制,其存在的意义就是为了能够方便的替换 TB 中的实例或者已注册的类型。一般而言,在搭建完 TB 后,我们如果需要对 TB 进行更改配置或者相关的类信息,我们可以通过...

详细讲述了芯片研发中必不可少的验证流程,UVM是一种通用验证方法学,本资料包括UVM的基本架构以及示例代码的详细讲解

年轻人的第一个UVM验证平台搭建——driver最初版本引入factory机制、objection机制和vitual interface之后 最初版本 `ifndef MY_DRIVER__SV `define MY_DRIVER__SV class my_driver extends uvm_driver; function ...

本发明涉及芯片设计的功能验证领域,尤其是一种基于UVM的总线验证方法。背景技术:随着集成电路工艺的不断进步,集成电路的规模和复杂度也在不断地提高,验证的难度也越来越大。在集成电路设计中,验证工作已经占到...

数字ic验证学习ing

标签: 数字验证

验证功能模块级功能子系统级功能 与 芯片级功能1.2. 验证层次1.3. 验证方法动态仿真静态检查虚拟模型硬件加速效能与性能1.4. 测试用例1.5. 覆盖率要求回归测试通过率代码覆盖率断言覆盖率功能覆盖率 1. 验证计划 ...

eda playground是一个适合学习的在线数字芯片验证平台,上面提供了快速搭建验证平台的脚本,本资源就是这个脚本的使用手册,建议配合https://www.doulos.com/knowhow/systemverilog/uvm/easier-uvm/的开源代码进行...

路科验证官网:路科验证 - 专注于数字芯片验证的系统思想和前沿工程领域 EETOP路科首页: EETOP - 路科验证 - IC验证培训 CSDN路科首页:CSDN - 路科验证 - IC验证培训 引言 用SystemVerilog和UVM写验证平台时,...

下一代验证方法学:UVM

标签: 验证方法学

下一代验证方法学:UVM,VMM和OVM的终结

sv中的子类和父类 在sv中,有如下两个类,child继承于parent。然后在test module中,正确转换的方法如下面所示。其中c1,c2,p1 都指向了同一个子类的对象c1。总结如下: 一个子类的对象是包括子类的成员变量,方法...

【UVM库v1.1源码】UVM是通用验证方法学的简写,本文件是UVM库v1.1源码,v1.1版本是市面上广泛应用的版本,研究源码有助于更深刻理解UVM机制,便于写出更好的芯片验证程序

1.软件安装 (1)下载安装questasim_10.6c; questasim10.6c下载地址: ... 安装:关闭win10杀毒软件和防火墙,双击安装包中questasim-win64-10.6c.exe进行安装,安装路径自选,安装路径最好不要有中文字体,一路...

芯片验证自学应该怎么入门,需要学什么? 我这一个月一直在想,怎么用最简单的话概括自己的学习,特地整理如下 芯片验证应该学什么: ☆☆☆☆☆第一重要的,就是linux操作。 因为芯片验证工程师每天的工作环境,...

UVM做的事情就是给提高验证环境的复用性,那么相对SV,UVM 为什么提高了复用性?一下几点将回答这个问题。 总结为以下几点: 1.各个模块的验证环境是独立封装的,对外不需要保留数据端口,因此便于环境的进一步集成...

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地