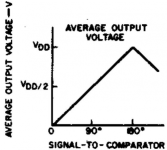

1 鉴相器(PD—Phase Detector)鉴相器是锁相环路中的一个关键单元电路,它负责将两路...(2)异或门鉴相器,这种鉴相器适合两路输入信号均为方波信号的锁相环电路中,所以异或门鉴相器常常应用于数字电路锁相环路中。(...

”锁相环环路滤波器计算公式“ 的搜索结果

用于高频接收器和发射器的锁相环 ——第一部分PLL的基本概念 本三部曲系列旨在全面概述锁相环(PLL)在有线和无线通信系 统中的应用。 第一部分将重点介绍有关PLL的基本概念,同时描述基本PLL 架构和工作原理...

欢迎使用Markdown编辑器 你好! 这是你第一次使用 Markdown编辑器 所展示的欢迎页。如果你想学习如何使用Markdown编辑器, 可以仔细阅读这篇文章,了解一下Markdown的基本语法知识。 新的改变 我们对Markdown编辑器...

fpga小白的学习之路

锁相环(PLL)基本原理 一、摘要 锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。本文将参考上述各种应用来...

锁相环及载波同步算法的研究数字化锁相环以及软件锁相环的原理都是基于最早的线性锁相环(模拟锁相环)的...载波同步主要采用环路进行自锁载频,锁相环是其关键部件,在对锁相环研究的基础上,对通信系统中载波同步...

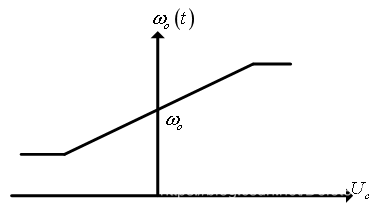

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中...

当环路输入信号与 VCO 输出信号的相位差改变时(这个相位差可以是零值,也可以是一个不为零的定值),在由鉴相器、环路滤波器、 VCO 组成的闭环电路的控制作用下,使得这个相位差维持不变。我们现在来分析一下。根据...

锁相环(PLL)低杂散方案设想初始版本

您好,冒昧的打扰您,我想要一下您出版的《锁相环技术原理的FPGA实现》、《数字通信同步技术》、《数字调制解调技术的MATLAB与FPGA实现》书籍的电子版,方便假期在家里学习锁相环及调制解调技术,您方便发一下么?...

此贴转载技术贴,原文地址已经不明了。如果原创作者或者知道原创出处的朋友们,可以告知一下,尊重原创。 一、SERDES的作用 1.1并行总线接口 在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口...

我以前写过篇博客,讨论了《锁相环电路设计与应用》书中提到的滞后超前型低通滤波器的特性。http://blog.csdn.net/liyuanbhu/article/details/7831863 不过当时没有仔细计算书后附录给出的曲线。最近有点空闲时间,...

一、SERDES的作用 1.1并行总线接口   在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。   &... 随着接口频率的提高,在系统同步...

简述DDS与FIR原理,并在Vivado工具链下用FPGA实现两者,适合初学者进行学习和练习

电荷泵锁相环的数字锁定检测电路应用分析----转载 作者:Steven Shi,Nick Dai 德州仪器 摘 要 电荷泵锁相环的锁定指示电路设计,常用的方法是在PFD 电路中通过检测经分频后的参考输入和本振反馈信号的...

推荐文章

- python入门(13)异常与文件_except filenotfounderror:-程序员宅基地

- Android面试攻略_详细了解在当今的社会里android工程师应具备什么的技能?并能详细说说自己的见解。-程序员宅基地

- Zendframework 1.6整合Smarty_setting private or protected class member is not a-程序员宅基地

- Qt-装饰者模式_qt装饰模式-程序员宅基地

- 新开普掌上校园服务管理平台service.action RCE漏洞复现 [附POC]-程序员宅基地

- 基于 Milvus 的音频检索系统-程序员宅基地

- 331、基于51单片机智能红外遥控暖风机温度无线蓝牙远程控制系统设计(程序+原理图+配套资料等)_红外感应暖风机自动控制系统设计-程序员宅基地

- Android自定义圆角矩形图片ImageView_android 矩形圆角imageview-程序员宅基地

- 又见回文 字符串-程序员宅基地

- switch的参数可以是什么类型?_switch的参数有哪些-程序员宅基地