”时序分析“ 的搜索结果

常用时序分析SDC 命令参考.doc

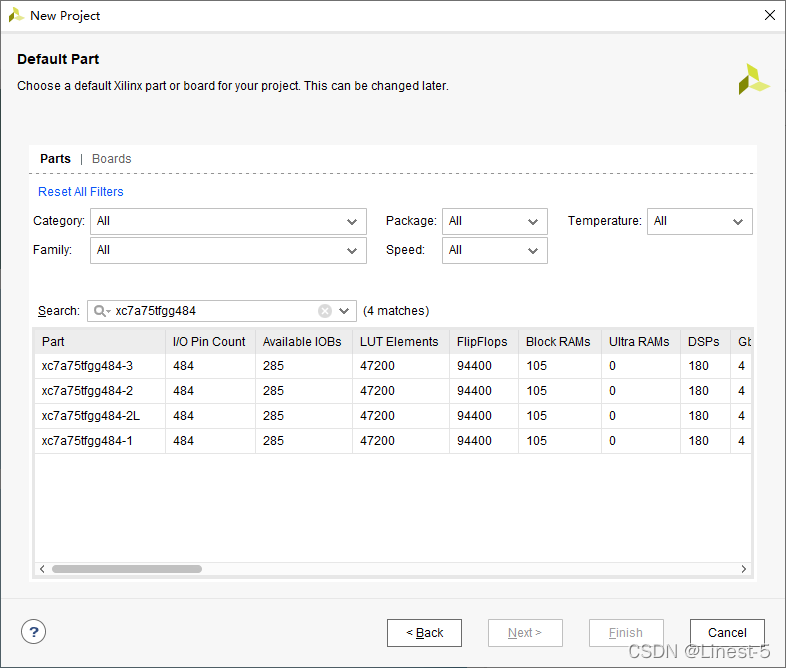

1.FPGA内部来说,常见的基本时序路径(即静态时序分析对象)有以下四类: (1)内部寄存器之间的时序路径,即reg2reg (2)输入引脚到内部寄存器的时序路径,即pin2reg (3)内部...

新手教程06:静态时序分析

标签: 学习

包含“静态时序分析(Static_Timing_Analysis)基础及应用.pdf“、“静态时序分析STA.pdf”、“系统设计中时钟、时序相关问题.pdf”

简要介绍STA和标准工艺库内容,对时钟,IO等进行约束的指令介绍,PVT

静态时序分析(Static Timing Analysis)基础及应用 ◎陈麒旭经典教程

本文介绍了不同复位的优缺点,比如同步复位,异步复位以及同步化的异步复位。

前两篇文章介绍了什么是亚稳态?以及静态时序分析,但那些终究还是理论,那么在实际工程中,如何分析时序路径呢?如何将理论转到实际呢?

静态时序分析基本原理和时序分析模型.pptx

华为静态时序分析资料,写的很好,很清楚,很适合时序分析的初学者

这篇文章详细讲解了I2C的时序、引脚定义等相关的内容,比较详细易懂

描述性时序分析,统计性时序分析,频域分析,时域分析,时序数据挖掘,时间序列挖掘(平滑法预测、趋势预测、季节性预测、符合型时间序列预测…)

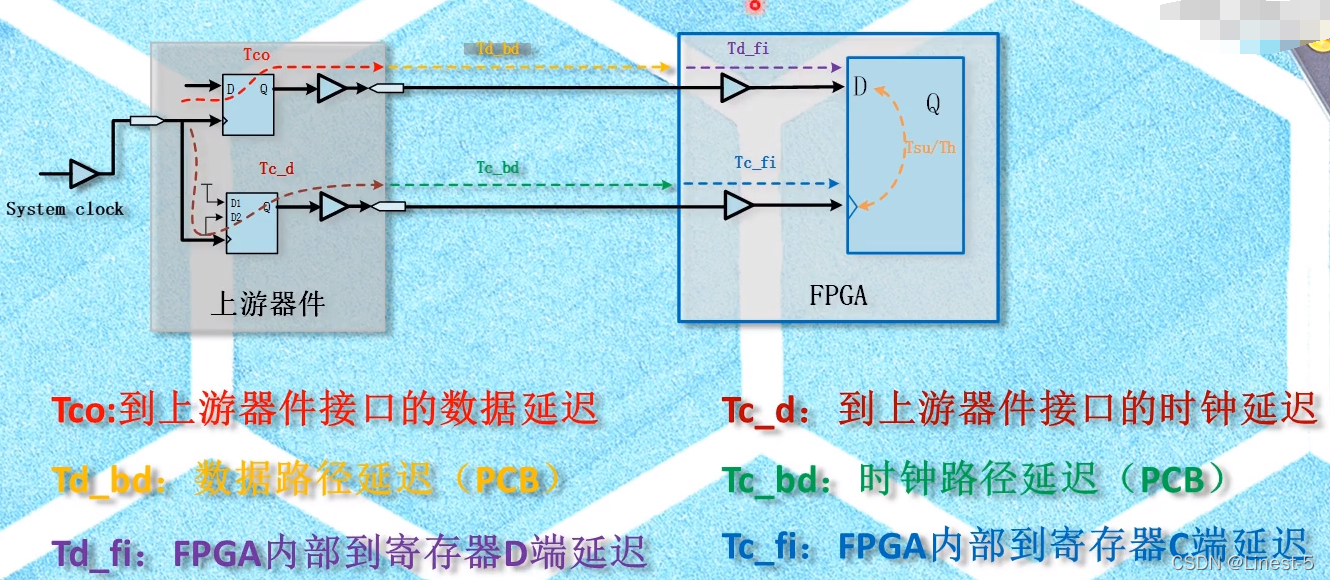

对于高速数字系统设计,时序分析尤其重要,特别是随着时钟频率的提高,留给数据传输的有效读写间隙越来越小,想要在极短的时间内让数据信号从驱动端完整地传送到接收端,就必须进行精确的时序计算和分析。...

这是一份详细的prime timing时序分析工具使用教程,英文原版讲解数字IC设计后端静态时序分析的理解和prime timing的使用

据个人理解区分静态时序分析和动态时序分析,是在于在分析电路时序时有没有输入激励。STA分析就是通过时序库文件给出的各条时序路径的延迟,来确认在每个FF上是否满足建立/保持时间。而DTA就需要给设计灌入激励在...

时序约束与时序分析系列博客,完整版PDF指导文件。博客地址: https://blog.csdn.net/qq_33486907/article/details/89380368

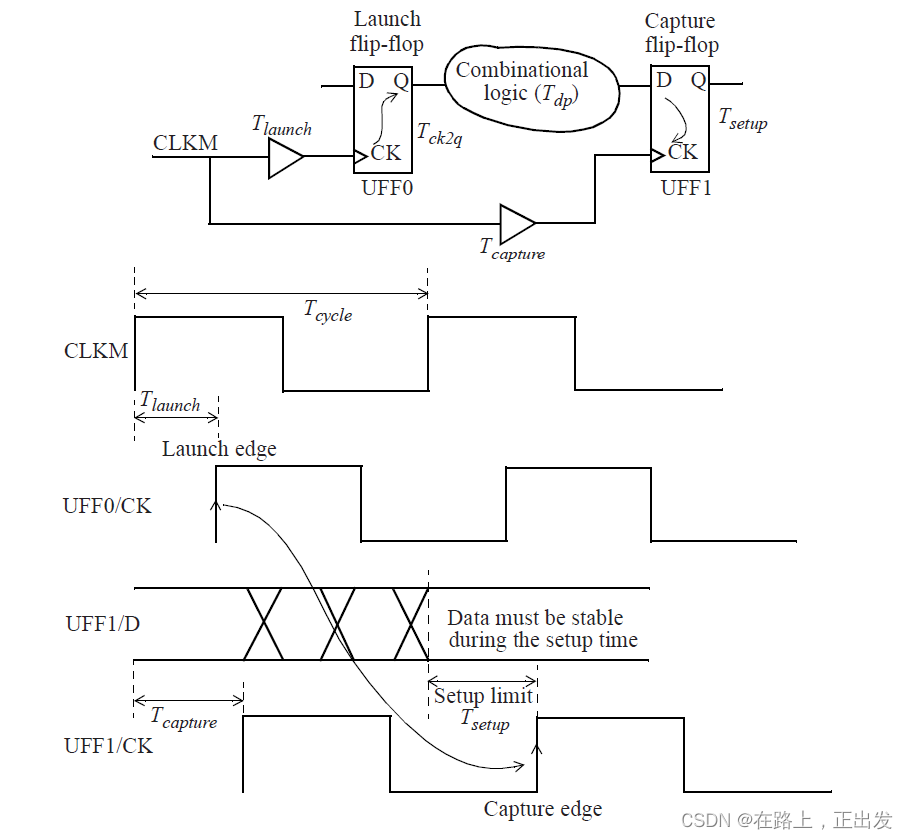

时序分析的题目是FPGA逻辑岗和数字IC岗最常考的题型之一,也是我们第一次讲解关于时序分析相关的题目,希望大家能够通过这道题解析和扩展对时序分析的概念、原理、公式、计算、应用都能够有一个初步的了解。...

推荐文章

- MacOS 系统成功安装 tensorflow 步骤_mac装tensorflow-程序员宅基地

- ES(Elasticsearch)7.6.1安装教程_安装elasticsearch-程序员宅基地

- spring boot>>RabbitMQ中间件发送验证码_basevo依赖-程序员宅基地

- uiautomatorviewer拉取手机竖屏却显示为横屏的问题_uiautomatorviewer方向倒了-程序员宅基地

- 加密技术简介-程序员宅基地

- 使用迭代器Iterator遍历Collection_.keyset().iterator().next()-程序员宅基地

- 日常Java练习题(每天进步一点点系列)_callable的call方法返回值-程序员宅基地

- 已解决Using TensorFlow backend.-程序员宅基地

- ring0下的 fs:[124]_nsfs124-程序员宅基地

- 高德地图打包后不能使用,高德导航View不显示,高德地图导航组件黑屏的问题;_amap.amapwx打包成安卓后无法使用-程序员宅基地