Verilog常用时钟激励方法

”常用的时钟激励“ 的搜索结果

FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路...

常用的有85M晶振、125M晶振等等。晶振通常与锁相环电路配合使用,以提供系统所需的时钟频率。如果不同子系统需要不同频率的时钟信号,可以用与同一个晶振相连的不同锁相环来提供。下面就让我们来看看如何选择晶振? ...

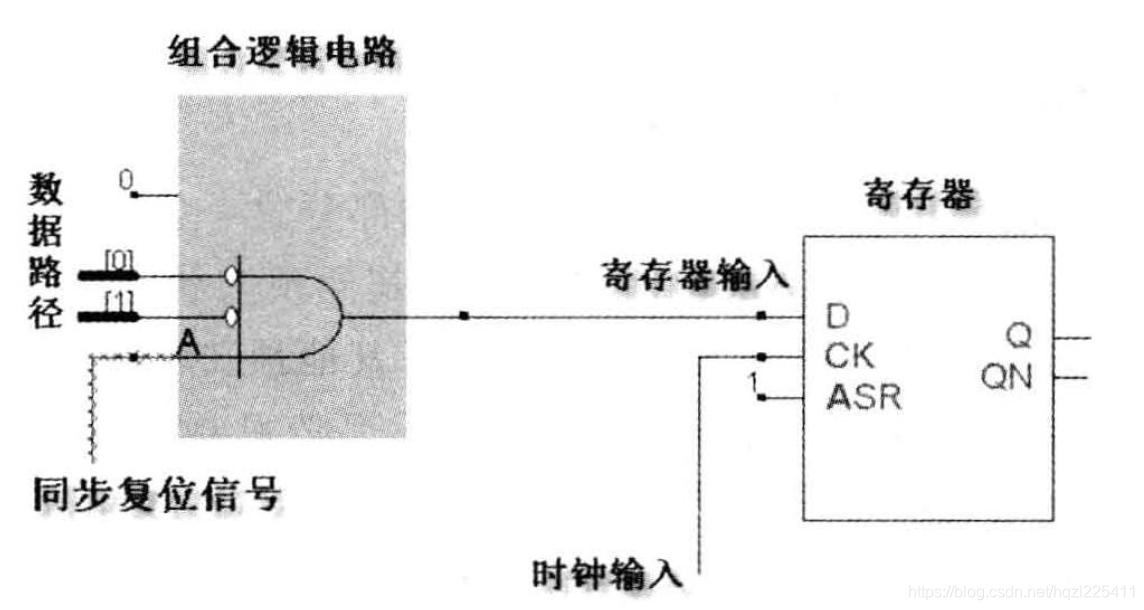

在FPGA设计开发中,复位激励(reset)是非常重要的,它能够保证设计在初始状态下正确工作。异步复位是最简单也是最常用的一种复位方式。在这种方式下,当复位信号置位时,设计的所有寄存器都将被重置至初始值。其中,...

常用的有85M晶振、125M晶振等等。晶振通常与锁相环电路配合使用,以提供系统所需的时钟频率。如果不同子系统需要不同频率的时钟信号,可以用与同一个晶振相连的不同锁相环来提供。下面就让我们来看看如何选择晶振? ...

文章目录前言时钟及时钟域时钟,时序逻辑的心跳时钟信...

一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟...

片上时钟控制器(On-chip Clock Controllers ,OCC),也称为扫描时钟控制器(Scan Clock Controllers,SCC)。OCC 是插在SoC上的逻辑电路。用来做DFT测试,基本原理是在 scan shift 模式下, 选通慢速的ATE 时钟,load ...

握手协议,保姆级教程

时钟,时序逻辑的心跳 在时序逻辑中,正是时钟信号将各个存储单元中的数据一级一级地推动下去,如果时钟信号突然停止,那么整个时序逻辑也将陷入瘫痪,因此,时钟就好像时序逻辑的心跳一样,那么重要却又平常的存在...

本文节选自《FPGA之道》,通过作者的讲解,一起看看时钟和时钟域的相关问题,下一篇博客再看看作者如何来解释跨时钟域问题。

本文将介绍如何在FPGA中编写有效的时钟激励,并提供相关的源代码示例。在FPGA设计中,时钟激励主要用于确定设计中各个时序元素的运行速度和时间约束。时钟信号的频率和占空比都对整个系统的性能和可靠性有着重要影响...

记住,在 FPGA 的开发中,时钟激励的稳定性和精确性至关重要,一定要仔细检查代码的正确性。在 FPGA 的开发中,由于时钟信号是整个系统的“心脏”,时钟激励是必不可少的一环。该代码表示在仿真开始时,先将时钟信号...

手动仿真在项目开发中是比较常用的,此时需要手动编写testbench文件。对于初学者来说,可能觉得编写testbench文件比较困难,但其实并没有想象的那么复杂,我们只需要按照testbench的结构,编写基本的激励文件还是...

Verilog第六章

标签: fpga开发

1) 产生模拟激励(波形); 2) 将产生的激励加入到被测试模块并观察其输出响应; 3) 将输出响应与期望进行比较,从而判断设计的正确性。 激励的产生 对于testbench,端口应当和被测试的mo...

原标题:电脑主板里的晶振才是网络时代发展的根源文章来源于,转载请注明!匆匆一年又一年,转眼间我已经度过了20个严寒酷暑,长大是件很有意思的事儿,不经意间就发生了,本来是这样一个人,然后突然间变成另外一个...

本文使用理想单元库和TSMC 28nm利用理想单元完成全速树形串化器、半速树形串化器、全速移位寄存器串化器,半速多级树形解串器电路及其仿真测试1、PLL型CDR:包括压控振荡器VCO、分频器DIV、电荷泵CP、鉴频鉴相器PFD...

2.局部时钟靠BUFR驱动,只在一个bank内用(使用的第二全局时钟资源)。第二全局时钟总线是通过软件布线得出的,所以硬指标肯定比不过全局时钟总线的,特别是当你在已经有80%以上的布线率的情况下,可能会出现约束第...

7. 在新增信号和时钟对话框中,为该信号指定一个名称,并选择信号类型(输入或输出)和数据类型(常用的有bit、bit_vector、integer等)。 8. 根据设计需求,设置信号的初始值。可以选择将信号初始化为一个常数,...

入门FPGA第一个多模块项目——时钟的实现

FIFO本质为RAM,分为同步FIFO(SCFIFO)和异步FIFO(DCFIFO),前者读写用同一个时钟信号,后者则使用双时钟读写。不过同步FIFO实际运用中较为少(可用做数据缓存),一般多用异步FIFO,因为在FPGA设计中,往往都是多...

第1章ISE系统简介11.1FPGA/CPLD简介11.1.1FPGA/CPLD的基本原理21.1.2FPGA和CPLD的特点71.2FPGA/CPLD的设计流程91.3ISE系列产品的特点111.3.1特点综述111.3.2ISE的新增特性121.4ISE6.x支持的器件141.5ISE的4个软件...

第1章ISE系统简介1.1FPGA/CPLD简介1.1.1FPGA/CPLD的基本原理1.1.2FPGA/CPLD的特点1.2FPGA/CPLD的设计流程1.3ISE系列产品的新特点1.3.1特点综述1.3.2ISE5.x的新增特性1.4ISE5.x支持的器件1.5ISE5.x的系统配置与安装...

推荐文章

- PortSwigger Authentication_portswigger 老是登录失败-程序员宅基地

- TKCTF-学校内部的校赛_{fbtsytyanowx}ns-程序员宅基地

- SSH-程序员宅基地

- Android Studio移动.gradle文件夹重新设置新路径_android studio .gradle换位置-程序员宅基地

- iOS 审核因为HealthKit被拒的解决方式_nshealth shareusage description 没有勾选被驳回-程序员宅基地

- Vue3 -- 基于Websocket实现简易聊天室_vue3聊天室排版-程序员宅基地

- 硬件大熊原创合集(2022/02更新)_反激电源mos管振铃现象-程序员宅基地

- Java基本数据类型/包装类/对象/数组默认值_java各类型默认值-程序员宅基地

- Qt5开发从入门到精通——第一篇概述-程序员宅基地

- Jmeter-Foreach控制器-循环变量的值传递给下一个请求_jmeter vars 下一次-程序员宅基地