测试平台是个没有输入输出端口的模块。仿真在一个模块设计中是很关键的步骤,而testbench是仿真的很好工具。

”testbench“ 的搜索结果

task和function说明语句分别用来定义测试模块当中的任务和函数,利用任务和函数可以把一个很大规模的程序分解成很多较小的任务和函数,非常便于Testbench的编写、理解以及调试,类似于C语言中的函数接口,输入、输出...

对于新手上手具有很大的帮助,内有常用的时序模型,可以用来时序仿真,功能仿真等

一本比较好的FPGA testbench编写英文书籍,对于初学者可以学习。英文资料相对中文资料讲的通俗易懂。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity counters is port( reset : in std_logic; cs : in std_logic; clk : in std_logic;...

Verilog Test Bench使用,可以学习学习!------------------------------------------------------------------------------------------------------------------------------------------------------------------...

1. 激励的产生对于testbench而言,端口应当和被测试的module一一对应。端口分为input,output和inout类型产生激励信号的时候,input对应的端口应当申明为reg, output对应的端口申明为wire,inout端口比较特殊,下面...

Testbench简介 仿真测试是FPGA设计流程中必不可缺的流程,尤其在FPGA设计规模和复杂度与日俱增的今天,简简单单写两三个模块的Verilog代码,直接上板调试的工作,现实当中几乎已经不存在了。从笔者实际工作经验来...

Verilog Test Bench仿真讲解,真心浅显易懂,希望大家喜欢。谢谢

基于Verilog的奇偶分频器设计源码及对应的testbench,供大家一起学习。

如何编写FPGA测试代码,XILINX官方资料

在资源管理窗口选中了 testbench 文件后,在当前资源操作窗显示的 ModelSimSimulator 中显示了 4 种能进行的模拟操作,分别是:Simu

教你如何写testbench对电路进行仿真测试

flash verilog 源码 testbench

1. 激励的产生对于testbench而言,端口应当和被测试的module一一对应。端口分为input,output和inout类型产生激励信号的时候,input对应的端口应当申明为reg, output对应的端口申明为wire,inout端口比较特殊,下面...

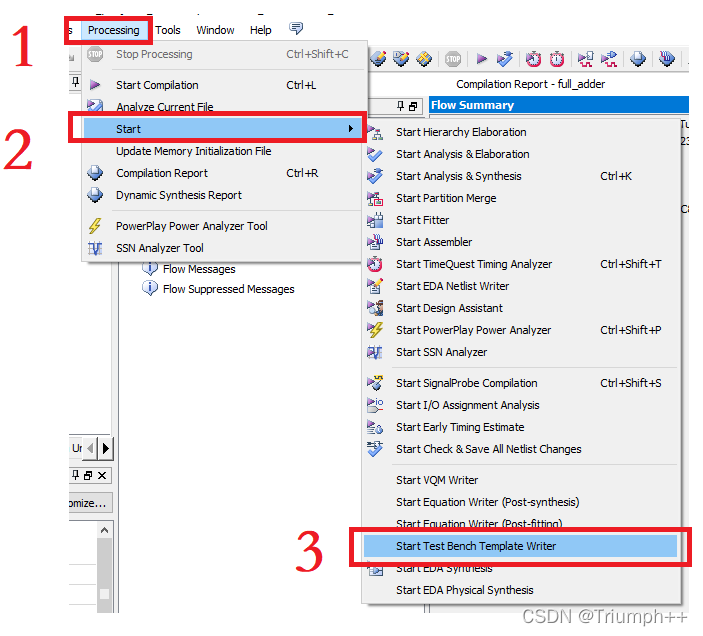

以后不需要再手写Testbech了,直接用这个就可以,输入你的verilog源码,直接就生成了可以测试的Testbench了。

UVM_TeatBench_For_ROM 完整的UVM TestBench,用于ROM验证Edaplayground链接: ://www.edaplayground.com/x/NvXM 博客链接: : 对于TB体系结构,有一个名为“ ROM TB ARCHITECTURE”的文件,TestBench还包括覆盖率和...

使用IVerilog进行编译—使用icarus verilog编译verilog文件修改testbench文件tb.v以更新模块DUT名称,用于读取输入激励数据的文件名称以及用于存储生成的输出的文件名称 iverilog -o output module.v tb.v vvp ...

需要学习systemverilog的可以看看,里面有6个lab可用于学习,代码和文档都有

试验台 探索新概念、架构和想法的项目

针对仿真的testbench设计,包括时钟的产生,数据的产生和交互

83优先选择器及testbench,包含源代码,测试可用。

verilog入门,自己跟着资料上写了一个101序列检测器,全部手敲的,顺便尝试第一次投稿!

针对FPGA软件测试过程中仿真测试和实物测试的不足,提出了一种基于仿真测试用例的实物自动化测试环境,将用于仿真测试的Testbench进行解析处理,形成能够用于FPGA实物测试的传输信号,通过执行器将此信号转换为作用...

Verilog Testbench与仿真 Verilog Testbench与仿真为通过软件验证Verilog语言设计实例的逻辑功能,需要编写 Testbench,也称为测试模块,并通过仿真软件ModelSim进行仿真。 ...test/confirm 用 HDL 写出来的测试文件...

但在testbench中是反过来的,输入是reg输出是wire。 原因:输入是自己设计的,我们要写寄存器,输出只需要读值 initial是仅在仿真之初被执行,一定先将变量初始化 initial begin clk = 1'b0; forever #5 ...

借鉴UVM的测试方法,在tb中将初始数据和结果数据写入txt文件,处理完成后,读出来,进行逐一对比,并打印结果。无需肉眼一一对比,将结果用计算机自动对比,减少人工工作量,提高了准确率。

常见的产生时钟和复位信号的testbench代码

推荐文章

- Linux 一台服务器上部署多个tomcat_liunx 一台服务器部署多个tomcat-程序员宅基地

- Numpy中numpy.rollaxis函数的理解_python numpy rollaxis-程序员宅基地

- java学习笔记_错误: 找不到或无法加载主类 com.it.duotai.dduotaitest-程序员宅基地

- JavaWeb入门必备JavaEE规范_java web 开发规范-程序员宅基地

- 《视觉SLAM十四讲》笔记——初识SLAM_视觉slam十四讲 stereo双目视觉-程序员宅基地

- STM32F103VET6+keil5+STM32CubeMX 按键控制灯_keil5按键控制stm32led-程序员宅基地

- list 与 numpy.ndarray互转_list转np.array-程序员宅基地

- WiFi基本知识总结 --- 通信框架及基础概念说明-程序员宅基地

- Linux安装deb软件包_linux 安装deb-程序员宅基地

- Leaflet从入门到放弃(一)——地图初始化_leaflet中文文档-程序员宅基地