AXI4_Full(一)总线说明

”axi4-full“ 的搜索结果

快速示例如何使用AXI4-Full接口(突发)为Zynq(ZedBoard)生成自定义AXI4IP_SystemVeri.zip

对xilinx中的AXI4_FULL IP核RTL代码进行逐行解析

axi_slave_ip代码仿真解读

AXI4-master源码分析

标签: AXI4

AXI4-master源码分析 AXI4-master源码分析 AXI4-master源码分析

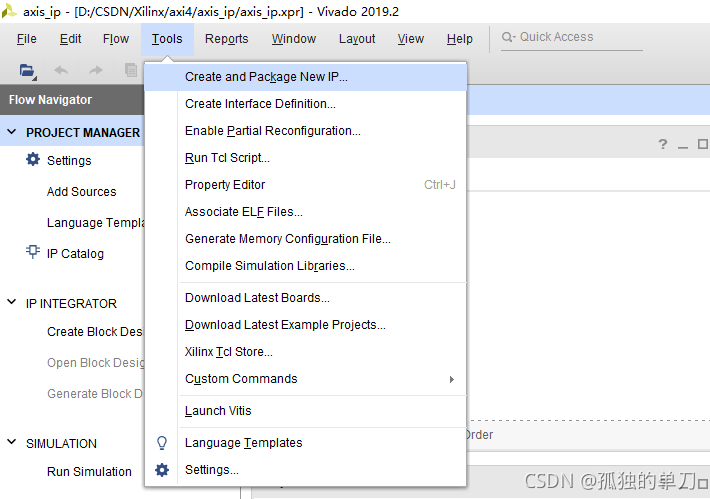

本文首先对AXI4总线协议进行了一个简单的介绍,然后使用vivado提供的模板创建了一个AXI4-Full Slave的接口,并生成了一个具有Master和Slave的代码实例,阅读该示例代码,进行修改后用于自己的项目。

1.简述 这儿遇到到ps端与pl端大量实时数据交互问题,实验了axi-lite总线,发现不行,实在太慢。接下来就只有axi-full总线了,但是这个好像比较复杂,所以先认真学习一下。

创建完毕后,vivado会自动生成block design,可以看见一个是自定义的master_full,另一个是官方生成的slave可以与其一起对应仿真。下图所示选项,测试的时候,数据通道位宽无所谓,只需要设置好主机以及AXI类型即可,...

AXI4总线系列文章汇总

基于Xlinx 的AXI4_Full手撕AXI_Full Master接口,采用Verilog实现,支持1~256的Burst_len,并对设计进行仿真验证。

AXI4-Full是一种高性能、低延迟的总线协议,它支持多个主设备和多个从设备之间的通信。在Vivado中,可以使用AXI4-Full总线协议来连接IP核和处理器系统。 相关问题: 1. AXI4-Full协议与AXI4-Lite协议有什么区别? 2....

今天自己编写了一个AXI4-FULL模块来发送自己的数据,仿真结果发现wdata,wvalid,wready等信号正常,是我想发送的数据序列。但从存储到的RAM中读取时,数据是间隔存在的。即我发送的信号序列是1,2,3,4.....78,79,80,...

本文首先对AXI4总线协议进行了一个简单的介绍,然后使用vivado提供的模板创建了一个AXI4-Lite Master的接口,并生成了一个具有Master和Slave的代码实例,阅读该示例代码,进行修改后用于自己的项目。

FIFO转AXI4-Full主机模块

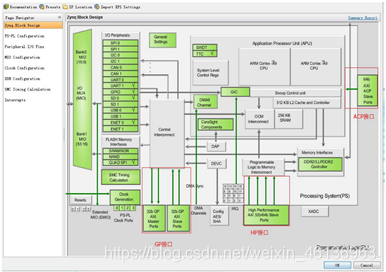

AXI(高级可扩展接口),是ARM MBA的一部分;AMBA:高级微控制器总线架构;是1996年首次引入的一组微控制器总线;...AXI4是学习ZYNQ的PL与PS交互通信的重要部分,必须弄懂原理时序,后续在进行实时整理更新。

推荐文章

- rotation matrix &reflection matrix-程序员宅基地

- [Layui]JS实现Layui树形表格treetable演示下载_layuiadmin下载 treetable-程序员宅基地

- 【Liunx笔记】Linux常用命令,值得收藏_常用linux命令笔记-程序员宅基地

- 微服务项目之电商--3.eureka集群搭建及eureka客户端详述及负载均衡Ribbon的使用和底层源码分析_高可用eureka集群+ribbon负载均衡-程序员宅基地

- Java字符串常量池-程序员宅基地

- Android 图片转动_android 图片转圈-程序员宅基地

- c语言.jpg图片转成数组_电脑使用图片转换器打开heic图片方法-程序员宅基地

- 2019年中国软杯-基于深度学习的银行卡号识别系统-程序员宅基地

- js清除HTML的input数据,js 清空 input file 的值的方法-程序员宅基地

- stm32H743 使用HAL库SPI读写外部flash失败原因_4线spi读不到flash-程序员宅基地