”Zynq“ 的搜索结果

FPGA 、ZYNQ和ZYNQ_Soc

linux3.0 device tree,包括zynq-7000,arm9,coretx-a9芯片级的所有外设驱动树,i2c,spi,dma,中断,gpio

适用于zynq7020的can调试,将库移植和软件移植可以测试can是否正常

ZYNQ 领航者FPGA开发板ZYNQ7020核心板+开发地板PDF原理图+主要器件技术手册,包括: 0-ZYNQ_7010核心板原理图_V1.5.pdf 0-ZYNQ_7020核心板原理图_V1.5.pdf 0-领航者ZYNQ底板原理图_V2.6.pdf AD9708.pdf AMS1117.pdf ...

前面文章分析了高速存储的各种方案,目前主流的三种存储方案是,pcie + switch高速存储方案,zynq高速存储方案,fpga高速存储方案。虽然三种高速存储方案都可以实现高速存储,但是fpga高速存储方案是最烂的,fpga...

仿真中有两个比较典型的 一个是Run Behavioral Simulation另一个是Run Post-implementation Timing Simulation,前一个是行为仿真,不存在时序前后的问题,后一个可以查看时序的先后(如输出信号和激励信号之间有...

zynq的PL向PS提供时钟和复位,利用蚂蚁T9+控制板开发

介绍了ZYNQAMP模式的搭建方法以及生成BOOT.bin文件的办法

本教程提供从vivado平台开始对硬件进行编程,然后倒入SDK进行嵌入式系统编程的全部详细过程,初学者可便利学习ZYNQ嵌入式系统的整体开发流程。并对SDK,vivado等软件的熟悉。

自己总结的ZYNQ程序固化的基本流程,包含从fsbl,等原理部分到具体配置流程的简述

总结起来,我们基于FPGA实现了一种类YOLO的轻量化CNN加速器,通过在zynq7020平台上的验证,证明了其在物体检测和特定识别任务上的优越性能。未来,我们将进一步优化算法和硬件架构,提高加速器的性能,并将其应用到...

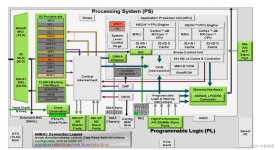

Zynq 芯片架构由嵌入式处理器(Processing System, PS)与可编程逻辑(Programmable Logic, PL),以及 PS 与 PL 之间的互联总线组成。本文主要介绍 Xilinx Zynq 芯片开发所使用的软件,包括 Vivado IDE 与 Xilinx ...

AXI-DMA:实现从 PS 内存到 PL 高速传输高速通道 AXI-HPAXI-Stream 的转换AXI-FIFO-MM2S:实现从 PS 内存到 PL 通用传输通道 AXI-GPAXI-Stream 的转换AXI-Datamover:实现从 PS 内存到 PL 高速传输高速通道 AXI-...

zynq7020芯片手册;ug585-Zynq-7000-TRM,zynq著名手册文档ug585;官网如果太慢,可以这里下载

ZYNQ7010 / 7020_AD9363 / AD9364 / AD9361 <<<<<<< HEAD 基于ZYNQ + AD936X的开源SDR硬件 ======= ac6507f2fe1946b64a4697f9ff1226f25c21065f 基于ZYNQ + AD936X的开源SDR硬件 <<<...

JTAG Boot(JTAG启动)是一种使用JTAG接口来启动设备的方法。JTAG(Joint Test Action Group)是一种国际标准测试协议,最初用于对芯片进行测试,现在已广泛应用于各种设备的调试和启动过程。在JTAG Boot过程中,...

一、CAN总线协议介绍 1.CAN是 Controller Area Network 的缩写(以下称为 CAN ),是 ISO 国际标准化的串行通信协议。 可以用来满足“多总线通信时,线束的数量过多”、“通过多个 LAN ,进行大量数据的高速通信”的...

ZYNQ实现yolov3-tiny算法,有各个模块实现的工程及全套代码,包括下面几个部分yolo_acc,yolo_conv,yolo_max_pool,yolo_upsamp,yolo_yolo这几个模块。

ZYBO是Digilent开发的以XC7Z010-1CLG400C为核心处理器的开发板,其主要功能包括有:1片32bit位宽,512MB容量的 DDR31个 HDMI port1个VGA source port1个(1Gbit/100Mbit/10Mbit) Ethernet PHY 与RJ45接口1个MicroSD ...

本文基于zynqmp的ps端pcie2.0 x4接口功能和SSD速度测试,其中pcie2.0x4的接口上连接ssd为nvme接口的ssd盘。本文设计vivado的pcie配置、uboot设备树修改、kernel源码修改以及基于dd命令进行NVMe的ssd读写速度的测试。...

Zynq AXIS:完整的DMA系统 此存储库包含使用Xilinx的Zynq FPGA建立基于DMA的项目所需的所有组件。 首先,有一个称为AXIS的硬件模块,可连接到高性能AXI接口端口。 其次,有一个Linux UIO驱动程序,可将低级AXIS控制...

SD卡启动允许设备从SD卡(Secure Digital Card)上读取引导加载程序或操作系统,从而启动系统。SD卡启动具有一些显著的优点,例如方便性、灵活性和可移植性。通过将必要的启动文件存储在SD卡上,用户可以轻松地更换...

我们还提供了已经加入了Preempt实时补丁的4.14.0-rt1-xilinx.tar.bz2内核,以及已经修订过针对4.14内核的ethercat-1.5.2-linux-4.14.tar.bz2源码。此外,我们还提供了编译好的内核uImage、ec_generic.ko、ec_master....

Zynq DMA Linux 驱动程序 该 Linux 驱动程序已开发为可在 Xilinx Zynq FPGA 上运行。 它是一个包装驱动程序,用于与低级 Xilinx 驱动程序 (xilinx_axidma.c) 对话,该驱动程序连接到在 Zynq FPGA 的 PL 部分中实现的...

采集外部设备的电压值,用FPGA内部自带的XADC

参考资料UG585第六章。

BOOT.BIN头其实就是BOOT.BIN文件前面的一段头部数据,并且这个头部数据是按照一定的格式组织在一起的,并且该头部数据能够被BootROM代码解析。在boot.bin文件中从地址0-0x8FF可以分为17个部分,每个部分都有一定的...

推荐文章

- 用好ASP.NET 2.0的URL映射-程序员宅基地

- C语言等级考试是把题目删了,历年全国计算机的等级考试二级C语言上机考试地训练题目库及答案详解(72页)-原创力文档...-程序员宅基地

- Microsoft Office显示正在更新无法打开的问题_正在更新microsoft 365和office-程序员宅基地

- 非常好的Ansible入门教程(超简单)-程序员宅基地

- 【Gradle-8】Gradle插件开发指南-程序员宅基地

- 使用PL/SQL Developer软件解锁_plsqldev表格锁怎么打开-程序员宅基地

- 【Windows Server 2019】Web服务 IIS 配置与管理——配置 IIS 进阶版 Ⅳ_iis默认路径-程序员宅基地

- 网络中的各层协议_发送消息时各层协议-程序员宅基地

- UCRT: VC 2015 Universal CRT, by Microsoft_vc15rt-程序员宅基地

- 关于EntityFramework 7 开发学习_entiry framework 7 书籍-程序员宅基地