Signal Tap ii逻辑分析仪的使用 具体要求 生成三角波并在Signal Tap ii中进行观察 设计说明 1.三角波的生成 采用sin3e工具生成三角波的mif文件,B是定义的数据位宽,Base是数据格式,采用16位数据格式,回车键...

”SignalTap“ 的搜索结果

在quartus中移除signaltap II文件,有时候我们用signaltap II 观测完波形后,为了节约资源和提高编译速度(signaltap II 是很消耗资源的,因我们的观测点实际在电路是生成了对应的节点的,),需要移除signal tap II...

FPGA设计FIFO IP核读写实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,对FIFO进行读写操作,写32个数据到FIFO中,再将写入的32个数据从FIFO中读出。其中包含了ModelSIm软件仿真和SignalTap II软件调试. ...

在写一个控制程序的时候,遇到一个量我想观测,就定义了一个寄存器,但是这组寄存器,在程序中有体现,signaltap II中却找不到,原来是这个信号跟模块的输入输出没有一点逻辑关系,只是我蹭了一个它的运算值。...

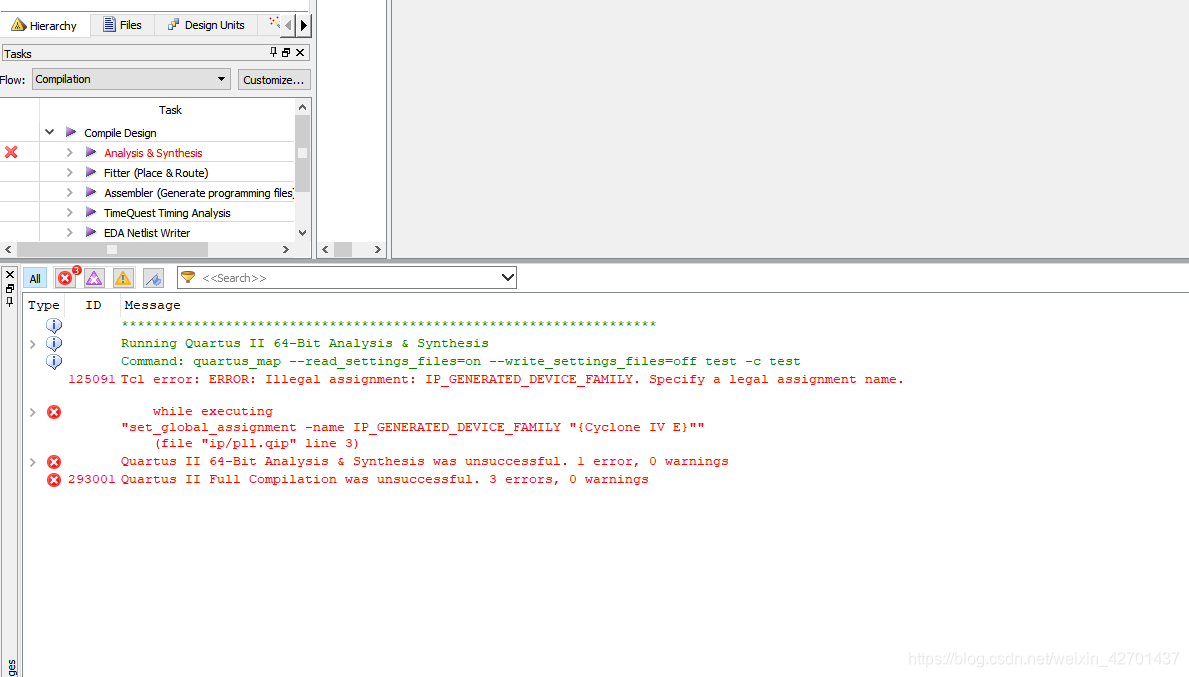

环境:Quartus ii13.1 开发板:EP3416Q240C8 任务:在

需要的点下载SignalTap.pdf。 本文由本人原创翻译,水平有限,仅学习所用,有错误请指正。 一、例子 我们使用如图1所示的verilog代码所实现的开关电路作为例子。这个电路把DE系列开发板上的前8个开关简单的和...

对于没有output的reg信号,Quartus在综合时也采用了最佳方式,因此,在SIgnalTap II中不能观察该信号。 解决方法: 对于reg信号则加/*synthesis noprune*/或者/* synthesis preserve */ 两者的不同之处在于: /*...

signaltap 笔记 时间 :2019年10月23日 地点 :苏州 前言 之前一直使用chipscope有四年时间,习惯了ISE的CDC使用,我个人的习惯是当FPGA编译时间小于十五分钟时,更愿意使用在线逻辑分析仪,这样的结果更真实,当然...

SignalTapII使用,在fpga设计调试中很好用的工具

Quartus 工程中移除signaltap的方法 问题描述:观察完信号之后,不想以后的quartus工程继续每次全编译都编译signaltap,加快编译时间 办法:在quartus的project navigator中右击step1.step,选择移除即可 ...

您需要 登录 才可以下载或查看,没有帐号?...TIM图片20200317122057.png (4.59 KB, 下载次数: 8)2020-3-17 12:21 上传答:可能的原因如下:1.该时钟确实是没有,即一直为0,或者一直为1。2. 该clk不...

SignalTap和SignalTap II是Altera(现在是Intel)公司的两个版本的逻辑分析器工具。这两个工具都用于调试和分析FPGA设计中的信号,但有一些区别。 SignalTap是早期版本的逻辑分析器工具,适用于使用Quartus II软件...

自己调的WM8731的程序,调了好久AD和DA转换全都通了,实现语音的采样与恢复

FPGA设计RAM IP核读写实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,构建RAM IP核实验,对RAM进行读写操作,写32个数据到RAM中,再将写入的32个数据从RAM中读出。 module Verilog_Ip_RAM ( CLK_50M,...

quartus——signal tap使用

我的Quartus – Signaltap的学习经历 1.认识Signaltap SignalTap II 是一款功能强大且极具实用性的FPGA片上debug工具软件,它集成在altera公司提供的FPGA开发工具Quartus II中。可以捕获和显示实时信号(Modelsim中...

Quartus中使用SignalTap观察被优化的reg与wire信号参考博客我的理解笔者使用的方法不足之处 参考博客 可以先看一下参考博客,讲的还算很详细。...

Signal Tap II有助于观察逻辑内部信号行为,可使不借助外部设备进行设计调试。(当然使用的前提条件是有硬件平台) Signal Tap II ELA 组成框图 采样获得的数据会存储在器件的存储器块中,通过JTAG下载线可以把...

小梅哥FPGA:ROM_SignalTap Ⅱ 目标: 1.将实现一组固定的数据(三角波形表)存储在FPGA中,并使用IP核构建的片上ROM进行存储,开发板上电后,系统开始从ROM中读取数据,并将数据直接通过并口输出,通过使用Signal...

版权声明:本文为博主原创文章,未经博主允许不得转载。 ... 在Quartusii中使用SignalTap II 抓取信号时,经常会遇到有些信号只在开机后...

打开QuartusII13.0软件,建立好工程后,先调用软件中的IP核ROM tools -> MegaWizard,进入如下界面

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地