”JK触发器“ 的搜索结果

J-K触发器的工作原理

标签: fpga开发

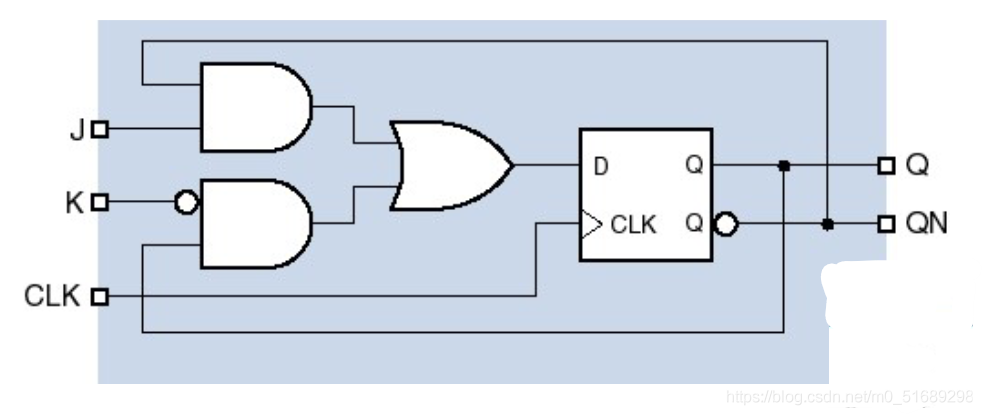

其区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。J = 1 K = 1 此时 Qn+1 = ~Qn,此时触发器从逻辑功能上完成翻转功能,此时J-K触发器类似于一个T触发器;J=0 K=0 此时 Qn+1 = Qn :此时触发器从...

JK触发器变为D触发器的实验仿真,实现JK触发器的拓展使用。

如您所见,要构建此配置,您需要一个基本的 JK 触发器电路,该电路与 S-R 触发器连接在一起。一旦时钟信号产生下降沿↓,从1变为0(1→0),就会触发从机部分,使Q输出反映主机的输出值。与需要完整脉冲的主从设计...

现态和次态现态: On触发器接收输入信号之前的状态次态: O(n+1)触发器接收输入信号之后的状态分类按电路结构和工作特点: 基本、同步、边沿按逻辑功能分:RS、JK、D和T(T')其他: TTL和 CMOS,分立和集成下面我会一一...

本文主要讲了jk触发器波形图怎么画?主从jk触发器波形图,下面一起来学习一下

数电实验报告JK触发器设计.docx数电实验报告JK触发器设计.docx数电实验报告JK触发器设计.docx数电实验报告JK触发器设计.docx数电实验报告JK触发器设计.docx数电实验报告JK触发器设计.docx数电实验报告JK触发器设计....

数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器.pdf数电实验—实验3—JK触发器....

数电课程设计、仿真文件、原理图、mltisim设计

FPGA程序设计实验报告JK触发器.pdf

RS触发器和JK触发器的Multisim实现学习教案.pptx

JK触发器及D触发器构成计数型触发器

标签: JK

基于Multisim14,绘制的JK触发器及D触发器构成计数型触发器仿真.

RS、D、JK触发器

JK触发器构成的十二进制计数器.ms14

主从JK触发器74LS76实验电路multisim源文件,multisim10及以上版本可以正常打开仿真,是教材上的电路,可以直接仿真,方便大家学习。

本文主要为jk触发器的逻辑功能表及波形图,下面一起来学习一下

该计数器是使用 Simulink Extras Flip Flops Library 中的四个 JK Flip-Flops 实现的。 作为输入,有一个恒定的 Count Enable。 如果它设置为 1,则计数器将工作,否则(在 0 上)不工作。 在第 16 个时钟节拍时,将...

维持阻塞结构的边沿JK触发器74LS109实验电路multisim源文件,multisim10及以上版本可以正常打开仿真,是教材上的电路,可以直接仿真,方便大家学习。

用JK触发器74LS73组成的四位移位寄存器实验电路multisim源文件,multisim10及以上版本可以正常打开仿真,是教材上的电路,可以直接仿真,方便大家学习。

中山大学软件工程数电实验jk触发器实现74ls194全部功能

JK触发器教案.pdf

标签: 技术

JK触发器教案.pdf

数字逻辑电路 JK 触发器.doc

标签: 计算机

数字逻辑电路 JK 触发器.doc 学习资料 复习资料 教学资源

寻找JK触发器清零端

标签: 十进制计数器

制作十进制计数器的辅助,十进制计数器-寻找JK触发器清零端

编写Verilog代码使之能正确描述下表所示的1bit JK触发器功能,其中Q+表示在时钟上升沿到来后的Q值。要求该触发器还具有异步复位的功能。

设主从JK触发器的原状态为1,按照图4.1(a)所给出的J、K、CP输入波形,画出触发器Q端的工作波形。解:此题信号K的某些跳变与CP脉冲的跳变发生在同一时刻,这是初学者容易感到疑惑的地方,所以要注意到,画Q次态波形时...

JK触发器的应用与仿真.pdf

标签: 技术

JK触发器的应用与仿真.pdf

Multism仿真

推荐文章

- confluence搭建部署_ata confluence-程序员宅基地

- SpringCloud与SpringBoot版本对应关系_springboot 2.1.1 对于的cloud-程序员宅基地

- 如何恢复硬盘数据?简单解决问题_磁盘恢复 csdn-程序员宅基地

- 苹果手机测试网络速度的软件,App Store 上的“网速测试大师-测网速首选”-程序员宅基地

- 教了一年少儿编程,说说感想和体验-程序员宅基地

- 22东华大学计算机专硕854考研上岸实录-程序员宅基地

- 如何用《玉树芝兰》入门数据科学?-程序员宅基地

- macOS使用brew包管理器_brew清理缓存-程序员宅基地

- 【echarts没有刷新】用按钮切换echarts图表的时候,该消失的图表还在,加个key属性就解决了_echarts 怎么加key值-程序员宅基地

- 常用机器学习的模型和算法_常见机器学习模型算法整理和对应超参数表格整理-程序员宅基地