FPGA调试SignalTap_II的简易使用方法

”FPGA调试SignalTap_“ 的搜索结果

AD9235FPGA编程 可AD采集信号 信号频谱检测 检测任意波形输入

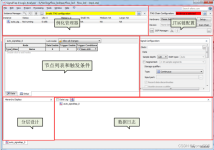

非常详细的图解SignalTap_II调试FPGA,非常详细的图解SignalTap_II调试FPGA非常详细的图解SignalTap_II调试FPGA

非常详细的图解SignalTap_II调试FPGA,非常详细的图解SignalTap_II调试FPGA非常详细的图解SignalTap_II调试FPGA 相关下载链接://download.csdn.net/download/fanglvguang/3574952?utm_source=bbsseo

伴随着EDA工具的快速发展,一种新的调试工具Quartus II 中的SignalTap II 满足了FPGA开发中硬件调试的要求,它具有无干扰、便于升级、使用简单、价格低廉等特点。本文将介绍SignalTap II逻辑分析仪的主要特点和使用...

使用SignalTap_II逻辑分析仪调试FPGA例 使用SignalTap_II逻辑分析仪调试FPGA例 使用SignalTap_II逻辑分析仪调试FPGA例 使用SignalTap_II逻辑分析仪调试FPGA例

对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下进行仿真和调试,开发板类型EP4CE15F17。主要包括一下几个部分: - FPGA的调试-虚拟JTAG(Virtual JTAG) - FPGA的调试-在线存储器内容...

FPGA设计PLL IP核实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,使用PLL IP核生成10M和20M时钟频率。 module Verilog_Ip_PLL ( CLK_50M,RST_N,LED1,LED2 ); input CLK_50M; input RST_N; output LED1...

介绍了可编程逻辑器件开发工具Quartus II 中SingalTap II 嵌入式逻辑分析器的使用,并给出一个具体的设计实例,详细介绍使用SignalTap II对FPGA调试的具体方法和步骤。

FPGA设计FIFO IP核读写实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,对FIFO进行读写操作,写32个数据到FIFO中,再将写入的32个数据从FIFO中读出。其中包含了ModelSIm软件仿真和SignalTap II软件调试. ...

具体操作如下,先选择好深度,将信号抓到,在信号附近鼠标右击,会有一个选项create signaltap II list file,点击保存后,在工程目录下会自动产生一个.txt文件,里面便是你刚抓的波形,只是全部以数字的形式出现...

中科院嵌入式的教程,关于SIGNALTAP 调试的一个例子

FPGA设计RAM IP核读写实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,构建RAM IP核实验,对RAM进行读写操作,写32个数据到RAM中,再将写入的32个数据从RAM中读出。 module Verilog_Ip_RAM ( CLK_50M,...

SignalTapII使用,在fpga设计调试中很好用的工具

FPGA设计ROM IP核读写实验,带ModelSIm和SignalTap II调试Quartus工程Verilog源码,构建ROM IP核实验,对ROM进行读操作,将ROM中的32个数据读出。 module Verilog_Ip_ROM ( CLK_50M,RST_N,readdata,address ); ...

小梅哥FPGA:ROM_SignalTap Ⅱ 目标: 1.将实现一组固定的数据(三角波形表)存储在FPGA中,并使用IP核构建的片上ROM进行存储,开发板上电后,系统开始从ROM中读取数据,并将数据直接通过并口输出,通过使用Signal...

随着芯片集成度的提高及封装技术的发展,系统设计与调试变得越来越困难,基于Quartus II软件自带的第二代系统级调试工具SignalTap II,采用EP4CE15F17C8的FPGA开发板为实验平台,以AD9280为核心进行数据采集系统的...

嵌入式逻辑分析仪Signal Tap II在FPGA设计中的应用、电子技术,开发板制作交流

1.为什么要用SignalTap ii: 在上板运行前都需要进行仿真,Modelsim 的使用可以使 FPGA 设计的许多错误扼杀在上板运行前,但这并不代表有了 Modelsim,我们的设计就天衣无缝了。实际上,在真正的上板运行时,...

Signal Tap II全称Signal Tap II Logic Analyzer,是第二代系统级调试工具,它集成在Quartus II软件中,可以捕获和显示实时信号,是一款功能强大、极具实用性的FPGA片上调试工具软件。传统的FPGA板级调试是由外接的...

modeisim的安装问题一定会有很多,主要问题出在环境变量的设置,大家根据破解说明一步一步做是完全可以破解的,笔者用的是modeisim-altera 10.1,在这里可贴上安装完后如何设置modeisim使每次编译完后自动仿真。...

中科院嵌入式的教程,关于SIGNALTAP 调试的一个例子 相关下载链接://download.csdn.net/download/kakasisi/1570555?utm_source=bbsseo

对于FPGA调试,主要以Intel FPGA为例,在win10 Quartus ii 17.0环境下进行仿真和调试,开发板类型EP4CE15F17。主要包括一下几个部分: - FPGA的调试-虚拟JTAG(Virtual JTAG) - FPGA的调试-在线存储器内容...

*问题描述:**在signaltap调试时遇到了一直报Program the device to continue的问题,检查连线和驱动都没问题。**解决方案:**将重新编译后的程序下载到板子上,再运行signaltap仿真。**原因:**重新编译后的程序,...

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地