”FPGA时序分析“ 的搜索结果

FPGA 之 时序分析

标签: fpga开发

XILINX 时序约束使用指南笔记 ——时序约束介绍 时序约束方法 时序约束原则等

FPGA的时序分析与约束需要设计者根据实际的系统功能,通过时序约束的方式提出时序要求;FPGA编译工具根据设计者的时序要求,进行布局布线;编译完成后,FPGA编译工具还需要针对布局布线的结果,套用特定的时序模型,...

FPGA时序分析约束

标签: fpga开发

静态时序分析(SAT) 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及...

小梅哥FPGA时序约束从遥望到领悟详解

正点原子FPGA静态时序分析与时序约束_V1.0.pdf

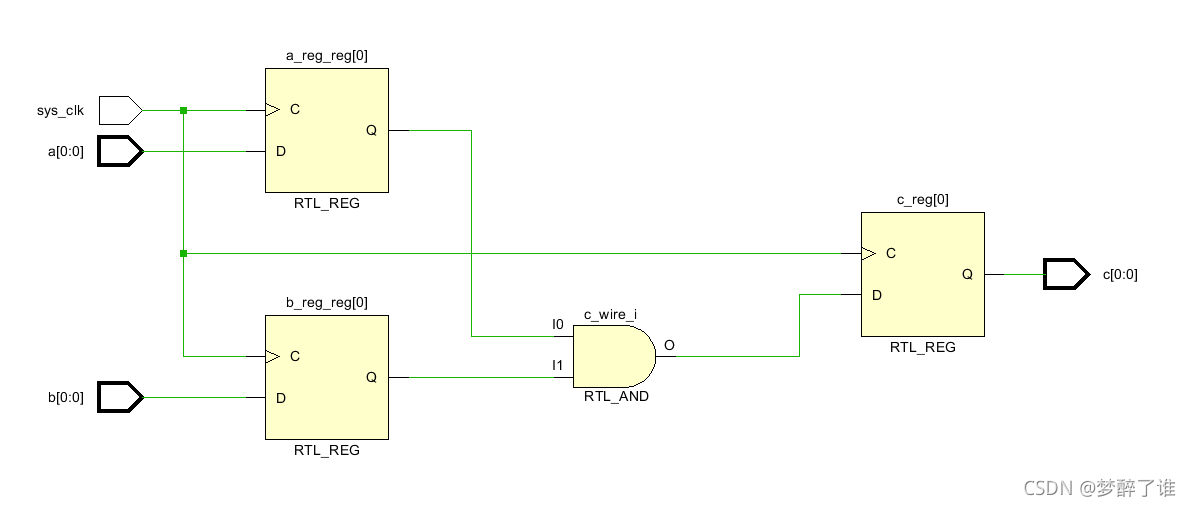

1.FPGA内部来说,常见的基本时序路径(即静态时序分析对象)有以下四类: (1)内部寄存器之间的时序路径,即reg2reg (2)输入引脚到内部寄存器的时序路径,即pin2reg (3)内部...

INTEL FPGA时序分析资料中文翻译版与英文原版资料。详细的介绍了FPGA时序分析的相关原理与分析方法。

FPGA时序分析、优化与约束

标签: fpga开发

本文中我们学习了时序分析,时序约束,时序收敛的含义,我们主要采用的时序分析方法是静态时序分析法,在后文中,我们将正式开始介绍如何进行时序分析。

FPGA时序分析入门

标签: fpga开发

FPGA时序分析与约束【二】

标签: fpga开发

本文主要介绍了FPGA中时钟的不确定性问题,FPGA中的时钟不确定性由2部分组成,时钟抖动和时钟偏移,时钟抖动由时钟内部产生,是时钟的固有参数,时钟偏移是由于时钟到达不同部分的时间不一致导致的,与FPGA的设计...

FPGA时序分析是指对FPGA设计中的时序约束和时序路径进行分析和验证的过程。时序约束是用来描述设计中各个信号的时序要求,如最大延迟、最小脉冲宽度等。时序路径是指信号在电路中从输入到输出经过的各个逻辑元件和...

本文我们介绍了时序电路中的时序问题,这是我们进行进一步时序分析内容学习的重要理论基础,首先我们介绍了D触发器相关内容,着重说明了建立时间和保持时间的含义和产生原因,然后引入了触发器的输出时序,最后介绍...

FPGA时序分析与约束参考工程

FPGA时序约束、时序分析[归纳].pdf

主时钟通常是FPGA器件外部的板级时钟(如晶振、数据传输的同步时钟等)或FPGA的高速收发器输出数据的同步恢复时钟信号等。

推荐文章

- 联邦学习综述-程序员宅基地

- virtuoso--工艺库答疑_tsmc mac-程序员宅基地

- C++中的exit函数_c++ exit-程序员宅基地

- Java入门基础知识点总结(详细篇)_java基础知识重点总结-程序员宅基地

- 【SpringBoot】82、SpringBoot集成Quartz实现动态管理定时任务_springboot集成quratz 实现动态任务调度-程序员宅基地

- testNG常见测试方法_idea_java_testng 测试-程序员宅基地

- Debian11系统安装-程序员宅基地

- Centos7重置root用户密码_centos7更改root密码-程序员宅基地

- STM32常用协议之IIC协议详解_正点原子stm32 iic-程序员宅基地

- 【视频播放】Jplayer视频播放器的使用_jplayer 播放amr-程序员宅基地