”CMOS传输门的边沿触发器电路结构及工作原理“ 的搜索结果

CMOS D触发器足主-从结构形式的一种边沿触发器,CMOS T型触发器、JK触发器、计数单元、移位单元和各种时序电路都由其组成,因此仪以CMOS D触发器为例进行说明。 图1是用CMOS传输门和反相器构成的D...

CMOS传输门组成的边沿JK触发器4027实验电路multisim源文件,multisim10及以上版本可以正常打开仿真,是教材上的电路,可以直接仿真,方便大家学习。

文献[1]指出,CMOS电路的基本触发单元是由传输门和或非门组成的主从结构,输入的数据由传输门引导,因此,对时钟脉冲的上升时间和下降时间就有一定的要求。但文献[l]对CMOS触发器在CP边沿的工作模式没有进行深人研究...

CMOS触发器CP边沿时间与器件参数的关系,用实验展现了CP边沿时间过长时出现的异变现象,分析了传输门在CP边沿的共同导通问题,提出了CMOS触发器在CP边沿工作的电路模型,推导了CP边沿时间的计算公式,完善和深化了...

双D触发器电路结构与工作原理2. CMOS传送门的边缘触发器 1. 双D触发器 电路结构与工作原理 用两个电平触发D触发器组成的边沿触发器,时钟相连 当CLK=0,触发器输出状态不变,FF1的状态与D相同 当CLK=1,上升沿到来...

边沿D触发器是一种常用的数字电路,可以利用CMOS传输门和CMOS与非门构造。具体实现步骤如下: 1. 将两个CMOS传输门(T1和T2)级联,其中T1的输入端连接D输入信号,T2的输入端连接T1的输出端,T1和T2的输出端分别...

5.4.1 D触发器电路结构与工作原理 简单的钟控D触发器的逻辑电路如图5.4.1所示。它也是在基本的RS触发器的基础上发展而来的。D触发器只有一个数据端。 下面结合其电路结构分析其工作原理。 当时钟...

CMOS传输门组成的边沿JK触发器4027实验电路multisim源文件,multisim10及以上版本可以正常打开仿真,是教材上的电路,可以直接仿真,方便大家学习。 相关下载链接://download.csdn.net/download/ailemony/13729392?...

双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器结构,如下图所示: 连个反相器连在一起,这就构成了一个双稳态器件,为什么是双稳态呢?我们现在就来分析一下: 由于...

CMOS边沿JK触发器由两个JK触发器和一些逻辑门组成,它的工作原理如下: 1. 输入信号:CMOS边沿JK触发器有两个输入端,分别是J和K。J和K分别代表输入信号的两个不同状态,可以是0或1。 2. 时钟信号:CMOS边沿JK...

触发器是时序逻辑电路的基本单元,用来存储1位2进制信息,具有记忆和存储功能,其信息由双稳态电路来保存。触发器位脉冲边缘敏感器间,分为上升沿敏感和下降沿敏感。触发器的种类很多,由D触发器,J-K触发器,T...

在FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的那些事。

前面说了CMOS器件,下面介绍一下锁存器跟触发器 1.双稳态器件 双稳态器件是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器 结构,如下图...

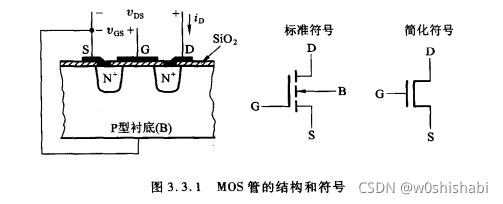

CMOS逻辑电路 目 录 1 PMOS管和NMOS管 3 2 CMOS管 4 3 非门 5 4 与非门 6 ...6 三态门 8 ...7 传输门 9 ...8 组合与时序逻辑电路 10 ...13 CMOS边沿D触发器 17 14 编码器 18 15 译码器 19 PMOS管和NMOS管 PMOS...

1、设计如图1所示用传输门构成的电平触发D触发器,和图2所示的边沿触发器 2、写出详细的电路原理分析; 3、编写Hspice网表文件,采用32nm的工艺; 4、进行电路瞬态波形仿真分析,进行功能验证; 5、改变负载,进行...

从CMOS到建立时间和保持时间芯片设计进阶之路——跨时钟域深入理解(三)------------------------------------------版权声明:本文作者: 烓围玮未首发于知乎专栏:《芯片设计进阶之路》转发无需授权,请保留这段...

CMOS触发器CP边沿时间与器件参数的关系,用实验展现了CP边沿时间过长时出现的异变现象,分析了传输门在CP边沿的共同导通问题,提出了CMOS触发器在CP边沿工作的电路模型,推导了CP边沿时间的计算公式,完善和深化了...

双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器结构,如下图所示: 连个反相器连在一起,这就构成了一个双稳态器件,为什么是双稳态呢?我们现在就来分析一下: 由于...

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地