常用数字设计仿真工具(Questa,VCS,IUS/Xcelium,Verdi等)使用入门-程序员宅基地

技术标签: SystemVerilog simulation Verilog IC设计和验证

目录

1. 前言

本文简要介绍一些主流的数字逻辑设计仿真器(比如说VCS, IRUN/Xcelium, ModelSim/QuestaSim等)的最基本用法。或许还会考虑一些设计验证辅助工具,比如说波形观测工具Verdi、Xilinx的Vivado等的基本使用方法。或许对入门者有些参考意义。(持续更新中)

2. QuestaSim基本使用方法

以下实验使用版本:Questa Sim -64 10.6c(Windows10)

基于以下代码源文件进行实验。

// hello_systemverilog.sv

`timescale 1ns/1ps

module tb;

initial begin

#100ns;

$display("@%0t: Hello, welcome to SystemVerilog world!",$time());

$finish();

end

endmodule2.1 命令行编译

命令行运行是指在命令行终端(windows cmd, 或windows terminal等)执行。

>> vlog -sv hello_systemverilog.sv

vlog是questasim的编译命令。“-sv”是指示vlog按照systemverilog语法进行编译。 编译后会生成一个库,由于以上没有指定,缺省的库名就是work。如果要显式地指定不同的库名,可以追加选项“-work libname”,初学者就不必去纠结这个了。

2.2 命令行运行

>> vsim -c -novopt work.tb

其中,“-c”表示在命令行运行,即不启动GUI(图形界面)。“-novopt”表示不做优化,在调试时通常使用这个选项,这个会使得仿真速度慢一些。work就是上一节编译生成的库,tb就是其中的仿真模型顶层,对应于以上module的module name。

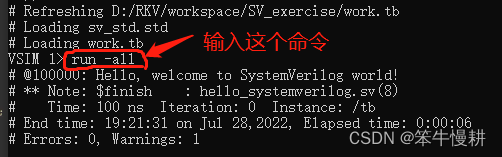

执行以上命令后,进入VSIM的命令行界面,提示符为“VSIM 1>”。

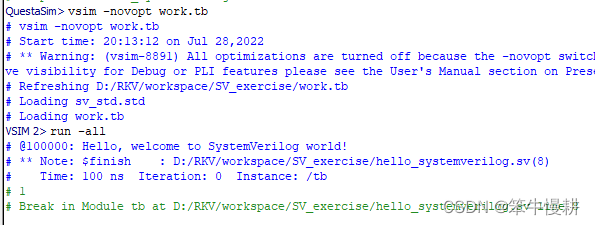

输入命令run -all就可以完成仿真。如下图所示:

也可以在run后面跟一个表示时间长度的参数。比如说“run 1ns”等。由以上源文件中可知,总的仿真时间为100ns,所以run后跟的时间长度参数大于等于100ns时其效果与“run -all”是相同的,都会跑完仿真并从VSIM命令行界面退出(退回到终端命令行)。如果小于100ns,则执行完命令后会继续停留在VSIM的命令行界面等待进一步的命令输入。

2.3 启动GUI进行仿真

上一节的命令中如果去掉“-c”选项,则会启动QuestaSim的图形界面。 当然,也可以显式地加上选项“-gui”

>> vsim -novopt work.tb

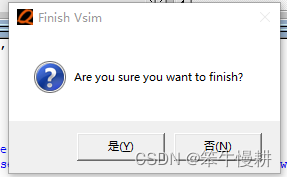

在弹出的QuestaSim-GUI的transcript窗口的命令行输入“run -all”,同样可以运行,如下图所示。

注意,在运行弹出的对话框,如果选择“是”会退出GUI,选择“否”则会继续停在GUI中等待下一步指令。

如果停留在GUI中,并且想重新执行一遍仿真,可以执行restart命令,然后运行run -all。注意,不执行restart而运行run -all,不会有任何效果,因为以上仿真已经结束(仿真时间已经前进到100ns处,再执行run也没有什么可运行的了)。restart相当于让仿真时间复位归零。

2.4 从GUI中进行编译运行

以上是从终端命令行执行QuestaSim编译运行命令启动QuestaSim-GUI。也可以直接先启动QuestaSim-GUI,在GUI中创建project、添加文件、编译、运行等。实际上毋宁说从GUI开始,是初学者最喜欢的方式吧。

双击QuestaSim图标启动QuestaSim-GUI,

从菜单栏选择File-->New-->Project:

选择“Add Existing File”并选择上面编辑好的源代码。右键选择文件从下拉菜单选择compile-->selected file:

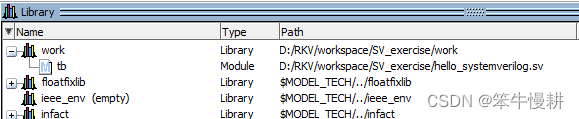

在library窗口看到编译生成的库work,及其中包含的tb:

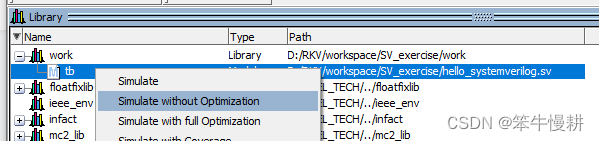

右键选择tb并下来菜单按如下图所示选择,即可启动仿真:

在下面的Transcript窗口会显示出等价的命令行命令“vsim -novopt work.tb”,然后停留在命令行等待指令,输入run -all执行仿真(与上面描述的相同),如下图所示:

2.5 dump波形

在图形界面仿真想dump信号波形观察的话,在执行run -all之前先执行以下命令即可:

VSIM 1> log -r /*

这条命令表示对所有信号进行波形dump,对于初学者来说,所接触的设计都比较小,就全部dump即可。以上命令选项就不赘述。当设计到大型设计的话,就要考虑有选择性的进行波形dump(话说回来,大型设计的话通常就应该采用vcs或者ius等了)。

当然,以上例码过于简单,没有波形观测的必要,这里就暂时不演示如何在QuestaSIm-GUI中观察波形了。

2.6 指定随机种子

>> vsim -c -novopt -sv_seed 0 work.tb

>> vsim -c -novopt -sv_seed random work.tb

可以用-sv_seed选项来指定随机化初始种子。 以上第一条语句是指定0作为种子,而第二条语句是指定每次运行随机生成种子。如果仿真程序中有随机因素,则第一条语句即便重复运行也会产生完全相同的结果,而第二条语句在重复运行时每次会产生不同的结果。随机化以及可控的随机化是仿真验证的一个非常重要的方面,值得仔细学习。

2.7 命令行指定testcase名

当一个testbench中存在多个testcase时,在运行仿真时需要指定所需要运行的testcase名,命令行格式如下:

Vsim [options] +TESTNAME=[testcase] work.tb

For example:

vsim work.tb -sv_seed $SEED -l sim.log +TESTNAME=smoke_test其中smoke_test为代表一个testcase的class name。 注意,不需要双引号。

2.8 其它常用选项

# 常用

-c # 使vsim运行在命令行模式,不启动图形界面,节省时间

-novopt # 不采用vopt优化,常和+acc配合使用,常用于调试阶段需要跟踪观测所有代码中出现的信号时-voptargs=acc # 采用优化编译,但是保留对所有信号可访问

-l <logfile> # 输出仿真的log文件

-do <dofile> # 开始仿真后运行tcl脚本(控制文件)

-L # 加载所需要的仿真库文件

-sv_seed [n | random] #指定随机种子

# 其它

-t # <ps or ns> 定义仿真时间精度

-g|G<name=value># 设置VHDL的generic参数值

-quiet # 关闭loading的信息

-coverage # 在仿真时产生代码覆盖率数据,功能覆盖率数据默认生成,与此项无关

-classdebug # 更多类调试功能

-solvefaileddebug # 使能输出随机化失败等更多调试信息

2.9 基于Tcl脚本的运行方法

当设计文件比较多,将所有仿真配置、命令、源文件等相关信息都写到一个Tcl文件中,能够大大提高工作效率。类似于windows中的批处理脚本、或者linux下的shell脚本或者Makefile等。以下介绍一个简单的QuestaSim仿真用Tcl脚本,在Windows和Linux下都可以使用。

set TB "tb_top"

set INCDIR "+incdir+../design"

set VCOMP "vlog -cover bst -timescale=1ns/1ps -l comp.log $INCDIR"

# clean the environment and remove trash files

set delfiles [glob work *.log *.ucdb sim.list]

file delete -force {*}$delfiles

# compile the design and dut with a filelist

vlib work

eval $VCOMP ../src/designfile1.v

eval $VCOMP ../src/designfile2.v

eval $VCOMP ../src/designfile3.v

eval $VCOMP -sv ./dut_pkg1.sv

eval $VCOMP -sv ./$TB.sv

# run a test

set TEST chnl_burst_test

set SEED [expr int(rand() * 100)]

vsim work.tb -sv_seed $SEED -l sim.log +TESTNAME=$TEST

run -all2.10 其它常用命令

vlog # 编译

vlib # 建立一个新的工作库/逻辑库

vmap # 映射逻辑库名到制定的目录

add wave # 将信号加入波形

run [x | -all] # 执行仿真(x表示仿真时间,-all 执行到结束,不带参数表示仅启动仿真)

quit # 退出仿真

3. VCS基本基本使用方法

Reference: VCS User Guide

3.1 编译

3.1.1 基本编译命令

verilog file编译基本命令:vcs top.v

需要编译多个文件时,可以将所有源文件按必要的顺序列在file.list中,然后调用命令:vcs -f file.list

对于SystemVerilog源文件的编译,需要加上选项-sverilog:vcs -sverilog top.sv

3.1.2 包含路径的指定

通常将一组相关联的类定义文件组成一个package,在package中include各类定义文件。比如说,Pkg.sv contains `include “file1.sv” ,`include “file2.sv.”

package pkg;

`include “file1.sv”

`include “file2.sv”

endpackage可以用以下编译命令进行编译,其中“+incdir”用于指定包含路径:

vcs -sverilog +incdir+filespath pkg.sv

3.1.3 其它常用选项

指定编译log文件,用“-l”选项:

vcs -sverilog -l compile.log top.sv

用“-timescale_override”选项指定全局time scale覆盖代码文件中的timescale定义:

vcs -sverilog -timescale =1ns/1ps -l compile.log top.sv #

vcs -sverilog -timescale_override =1ns/1ps -l compile.log top.sv #覆盖源代码中的仿真时间单位和精度,不推荐使用,会把模型的时间单位覆盖,可能导致模型功能错误

-timescale与-timescale_override的区别?

改变参数定义和设置:+define+LENGTH=10

vcs -sverilog +define+LENGTH=10 -timescale =1ns/1ps -l compile.log top.sv

对于UVM编译使用: -ntb_opts uvm-1.2

vcs -sverilog -ntb_opts uvm-1.2 +define+LENGTH=10 -timescale_override =1ns/1ps -l compile.log top.sv

debug选项:-debug_all

vcs -sverilog ntb_opts uvm-1.2 -debug_all +define+LENGTH=10

-timescale_override =1ns/1ps -l compile.log top.sv

代码覆盖率仿真选项: -lca -cm line+cond+fsm+tgl+assert -cm_tgl mda

vcs -sverilog ntb_opts uvm-1.2 -debug_all +define+LENGTH=10

-timescale_override =1ns/1ps -lca -cm line+cond+fsm+tgl+assert -cm_tgl mda -l compile.log top.sv

如果存在多个top module,可以通过-top指定top module进行仿真。在调试阶段特别方便。

vcs –sverilog design.sv –top work.tb1

-

+warn=noxxx选项:用于禁用特定的警告信息。例如,"+warn=noDNF"将关闭关于DNF表达式的警告。

3.1.4 vcs选项一览表

更全面的vcs选项一览表参见:[VCS]VCS常用命令詳解

3.2 vcs两步仿真

vcs的两步仿真是指,先用vcs命令编译生成一个simv文件(对应于下面三步仿真法中的compile和elaboration两个步骤的处理合二为一),再执行这个sim文件进行仿真。如下所示:

# Two-step Flow

# Compilation

% vcs [compile_options] Verilog_files# Simulation

% simv [run_options]

The two-step flow is supported only for Verilog HDL and SystemVerilog designs.如果设计中还存在VHDL的话,需要使用三步仿真法。主要原因在于,对于VHDL和Verilog所需要的Analyze命令是不同的,分别是vhdlan和vlogan。在两步仿真法中(由于Analyze or Compile和Elaboration合并在一起处理)缺省地是使用vlogan,所以无法支持VHDL仿真。

3.3 vcs三步仿真

vcs的三步仿真是指分编译(Compile or Analyze)、elaboration、和执行仿真三步执行。基本使用方法如下所示:

#Three-step Flow

#Analysis

#Always analyze Verilog before VHDL.

% vlogan [vlogan_options] file1.v file2.v

% vhdlan [vhdlan_options] file3.vhd file4.vhd#Elaboration

% vcs [elaboration_options] design_unit#Simulation

% simv [run_options]

以下是用Makefile(本Makefile取自路科验证课程示例文件)实现的vcs三步仿真flow所示。分别执行make comp, make elab和make run执行三步仿真法的三个步骤。

#############################

# User variables

#############################

TB = tb1

SEED = 1

DFILES = ../mcdt/v1/{arbiter.v,slave_fifo.v,mcdt.v}

VFILES = $(TB).v

#############################

# Environment variables

#############################

VCOMP = vlogan -full64 -sverilog -timescale=1ps/1ps -nc -l comp.log

ELAB = vcs -full64 -debug_all -l elab.log -sim_res=1ps -fsdb

RUN = $(TB).simv -l run.log -sml +ntb_random_seed=$(SEED)comp:

$(VCOMP) $(DFILES) $(VFILES)elab:

$(ELAB) -top $(TB) -o $(TB).simvrun:

$(RUN)

当然,当一切都调试完毕后,也可以直接一条命令执行完事:

make comp elab run

3.4 fsdb波形输出选项

vcs仿真中要输出fsdb波形,需要以下两方面的代码和设置。

(1)testbench文件中需要追加fsdb波形dump命令,示例如下:

//6. FSDB Waveform dump.

initial

begin

begin

$fsdbDumpfile("./top.fsdb");

$fsdbDumpvars(0,tb);

end

end(2) 在vcs命令行添加“-fsdb选项”,如以上Makefile中的ELAB命令所示:

ELAB = vcs -full64 -debug_all -l elab.log -sim_res=1ps -fsdb

当然,这个选项也可以修改一下,改为可以在命令行指定以便于在执行make命令开启和关闭fsdb波形输出。

3.5 ucli

3.5.1 基础介绍

Unified Command Line Interface (UCLI) 提供了与VCS交互仿真的控制命令,即与VCS的命令行输入接口。UCLI的命令是基于Tcl脚本语言进行编写的,也就是说可以编写Tcl脚本来实现:

- 控制仿真

- dump fsdb或者vpd波形文件

- 保存或恢复仿真状态

- force或release某个信号

- 使用breakpoints或scope以及内建宏等信息对设计进行调试

因此可以很灵活的进行调试和仿真控制。

基本使用方法:

simv -ucli -i xxx.tcl这里我们吃进去一个xxx.tcl文件,其中包含了想要的UCLI命令。

3.5.2 常见命令

VCS有命令行模式和图形模式,图形模式使用的是DVE,命令交互模式使用的是ucli。

vcs中要调用ucli接口,执行脚本,必须在compile的时候,加入debug的权限:-debug,-debug_pp,-debug_all,-debug_access,-debug_region。在run的时候,指定vcs -ucli [run_option],需要在编译时加入参数以开启ucli,否则ucli交互时只能使用简单的 ’run’、 ‘dump’、 'quit’命令。

推荐编译时添加参数如下:

‘-debug_access<+option>’ 对系统进行调试

‘-debug_access+classdbg’ 用于测试台调试

‘debug_access+all’

ucli提供的命令:

call,调用verilog或者vhdl中的system task;

stop,设置断点;

abort (中止评估宏文件)

ace (评估模拟模拟器命令)

alias 为命令创建别名)

assertion 断言(SVA / PSL)相关命令)

call 执行Verilog系统任务/功能,Verilog PLI任务/功能或VHDL外部过程)

cbug 对C,C ++和SystemC源文件的调试支持)

checkpoint 检查点/在当前/给定时间加入仿真设计)

config 显示/设置配置变量的当前设置)

constraints 显示设计信息,禁用/启用/添加/删除/更改约束,或提取约束的测试用例)

debug

coverage 评估覆盖命令)

detach_sim 从Verdi脱离simv,然后回到UCLI)

do 评估一个TCL(宏)脚本; “源” TCL命令的超集)

drivers 获取信号/变量的驱动程序信息)

dump 创建/操作/关闭转储值更改文件信息)

finish 让工具完成,然后将控制权返回给UCLI)

force 强制或将值存入信号/变量)

fsdb 适用于VCS(-MX)的Debussy FSDB命令集)

get 获取信号/变量的值)

helpdoc 修改或扩展ucli帮助页面)

listing 显示源文本)

loaddl 在模拟器空间中加载/卸载用户的动态对象

loads 获取信号/变量的负载信息

lp_show 本机低功耗(NLP)相关命令

memory 从文件加载/写入文件的内存值,或使用给定值初始化内存

msglog 设计和测试平台静态和动态数据记录

next 推进工具逐步完成任务和功能

onbreak 指定在宏到达停止点时运行的脚本

onerror 指定在宏遇到错误时运行的脚本

onfail 指定在宏遇到故障时运行的脚本

pause 暂停执行宏文件

power 电源统计相关命令(SAIF):

release 从使用“ force”分配的值中释放变量

report_timing 将实例的计时信息报告给指定的文件或控制台

report_violations 设置各种与xprop相关的报告违规

restart 重新执行工具; UCLI将使用以前的设置返回到零时间

restore 恢复保存在文件中的模拟状态

esume 恢复执行宏文件

run xx 运行xx时间后停止,不推荐使用

run 运行仿真直到遇到$stop或者设置的断点

run -posedge xx 运行到信号xx的上升沿停止

run -change xx 运行到信号xx变化时停止

saif 交换活动交换格式相关命令

save 将模拟状态保存到文件中

scope 显示当前的顶层

scope xxx 进入xxx模块

scope -up 回到上一层

search 搜索名称与指定模式匹配的设计对象

senv 显示一个或所有synopsys :: env数组元素

sexpr 评估工具中的表达式

show 显示当前模块的信号及子模块

show xxx -value -radix hex/bin/dec 以特定形式显示信号值

stack 显示线程信息或移动调用堆栈

start 开始执行工具

start_verdi 从UCLI提示符启动Verdi

status 显示宏文件堆栈

step 推进工具一条语句

stop 显示已经设置的断点

stop -posedge xx 在信号的上升沿设置断点

stop -condition {信号表达式} 在信号表达式为真的地方设置断点

stop -delete xx 删除断点xx,xx为断点数字编号

tcheck 启用/禁用指定实例/端口的定时检查

Tcl Tcl内置命令的帮助

thread 显示线程信息或移动当前线程

unalias 删除一个或多个别名

virtual 创建,删除或显示虚拟对象

xprop 设置或查询xprop合并模式

3.5 VCS与VCS_MX的区别

VCS_MX为mixed hdl仿真器,支持vhdl+verilog+sv的混合仿真。VCS只支持verilog, sv。在feature上唯一的区别在于对vhdl的支持。如果没有vhdl的设计的话或许VCS好些,速度快些。

4. IUS/Xcelium基本使用方法

4.0 帮助查询方法

irun -helpall | grep "word of interest"

比如说要查询关于ieee1364的仿真选项,可以输入命令如下:

$ irun -helpall | grep "ieee1364"

可以得到以下反馈信息(意思是按照IEEE1364标准报告错误):

-ieee1364 Report errors according to IEEE 1364 standards

4.1 基本使用方法

irun +access+rwc helloworld.v -timescale 1ns/10ps

irun -sv +access+rwc helloworld.sv -timescale 1ns/10ps

irun -sv +access+rwc helloworld.sv -timescale 1ns/10ps -seed 42

irun -sv +access+rwc helloworld.sv -timescale 1ns/10ps -seed random

irun -sv +access+rwc helloworld.sv -timescale 1ns/10ps -svseed 42

irun -sv +access+rwc helloworld.sv -timescale 1ns/10ps -svseed random

...

4.2 seed与svseed的区别

查询irun的帮助信息可以得到:

-seed <seed> Set the seed value for SystemVerilog and Specman

-snseed <seed> Pass seed value to Specman

-svseed <seed> Set SystemVerilog default RNG seed

对于systemverilog testbench,seed和svseed没有差别。都是用于指定初始随机种子。<seed>如果是数字的话,则表示用该数字作为随机种子;如果是random的话,则表示随机生成一个数作为初始随机种子。

指定确定的随机种子使得仿真结果可以再现,为调试提供了巨大的遍历。

4.3 Xcelium

Xcelium(xrun)是cadence最新的仿真工具,Incisive(irun)的升级版本。

【单步仿真】

xrun默认是单步仿真

>> xrun add.v //自动完成comp , elab ,sim

【三步仿真】

>> xrun -compile add.v // compile

>> xrun -elaborate add.v //elab, 生成可执行代码

>> xrun -R // 自动识别snapshot并执行

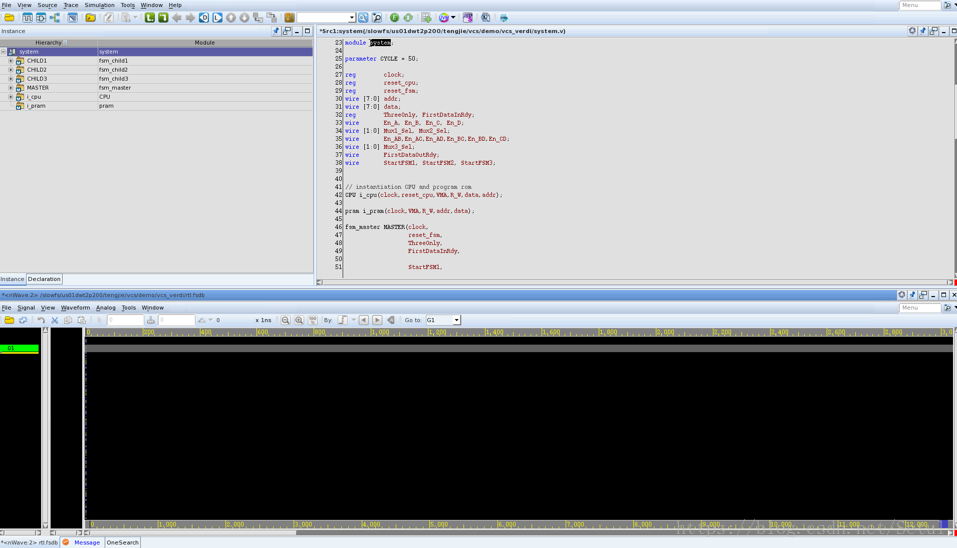

5. Verdi基本使用方法

5.1 verdi直接打开代码

verdi -f filelist.f -top rtl_top

verdi可以通过上面指令直接打开没有编译的代码,其中rtl_top表示rtl顶层模块。

5.2 kdb选项

kdb选项是vcs选项,在进行vcs仿真时可以加入kdb选项,vcs仿真会生成verdi的库文件,通常库文件为sim.daidir,库文件里面包含相应代码信息;利用库文件verdi可以快捷打开rtl代码而不需要重新编译。verdi利用daidir打开代码办法(以下两种均可打开RTL代码):

verdi -dbdir simv.daidir &

verdi -simflow -simBin simv &

5.3 verdi直接打开波形

verdi -ssf top.fsdb -arch32 -nologo &

-ssf表示指定波形文件。

5.4 verdi打开指定的restore文件

verdi -sswr fliename.rc

verdi可以通过以上指令,指定波形restore文件,可以将已保存的信号恢复。

而restore文件可以在verdi-gui中以如下方式保存:

当然加载restore文件也可以在这个菜单下进行(“Restore Signal”)。

5.5 添加波形观测信号

5.5.1 方法1

在波形区的左边是有G1, G2,。。。的分组的,方便对信号进行分组观测,双击可以将该组别的信号折叠起来。组名可以修改。如果现有的组中都有信号加入的话,verdi会自动生成一个新的空组。

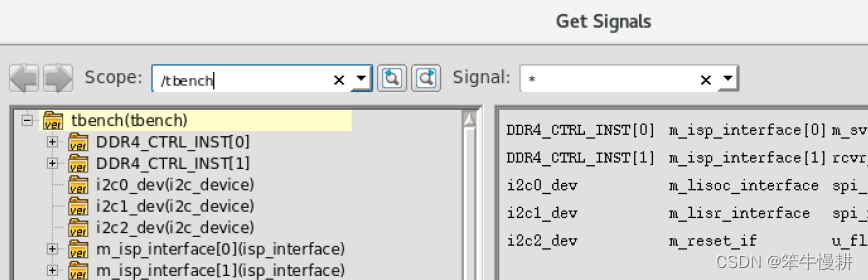

如下图所示的窗口下半部分为波形窗口(假定已经载入了波形),点击波形按钮,然后选择所要观测的信号加入即可。

如果想在某一组中添加信号,如G1,则单击G1, 然后点击键盘上的G,即可出现下面的对话框。该对话框左边是文件,右边是文件中的信号,可以通过下边的filter选择输入信号还是输出信号等等,这样也可以显示某信号的波形。

5.5.2 方法2

在右上代码区选中一个或多个信号,使用Ctrl+w即可将该信号的波形显示在下方的波形区。

5.5.3 方法3

File--> Restore Signal,然后选择之前已经保存好的*.rc文件即可。

6. 编译文件指定方式

参见https://blog.csdn.net/chenxy_bwave/article/details/130893972

7. fsdb波形dump

7.1 vcs环境变量设定

首先要把FSDB dumper库的路径添加到LD_LIBRARY_PATH环境变量, Shell命令格式如下:

setenv LD_LIBRARY_PATH ${LD_LIBRARY_PATH}:${NOVAS_HOME}/share/PLI/VCS/LINUX64注意:如果使用的是32位Linux,需要把LINUX64替换成LINUX。

然后在vcs的命令行添加 “ -fsdb ” 参数。

7.2 irun环境设定

将verdi的PLI库路径加入环境变量LD_LIBRARY_PATH:

setenv LD_LIBRARY_PATH ${LD_LIBRARY_PATH}:${VERDI_HOME}/share/PLI/IUS/LINUX64注意与vcs的路径的区别在于:VCS的是/share/PLI/VCS/LINUX64,Irun的是 /share/PLI/IUS/LINUX64。

7.3 Testbench中植入波形dump命令

这里以fsdb格式波形的dump为例进行说明。

首先需要在testbench的顶层植入以下代码块(这个与使用何种仿真器无关)。

initial begin

if($test$plusargs("FSDB_ON")) begin

//记录波形,波形名字.fsdb,也可以用字符串变量的方式设置为以testcase命名的文件名

$fsdbDumpfile("top.fsdb");

//0: 当前级及其下面所有层级,如top.A, top.A.a,所有在top下面的多维数组均会被dump

//1: 仅仅dump当前组,也就是说,只dump top这一层的多维数组。

//+all参数,dump SV中的struct结构体

$fsdbDumpvars("+all");

//也可以向以下这样指定某个模块进行波形dump,对于大型系统仿真来说这个很重要

$fsdbDumpvars(0,tb_top.u_DIGITOP.u_BB_TOP);

$fsdbDumpSVA(); //将assertion的结果存存储到fsdb中

$fsdbDumpMDA(0, top); //dump memory arrays

//以上仅为fsdbDump family的一些常见用法,其它所有各种用法可以查阅相关手册

end

end

7.4 仿真命令行参数指定

以上代码段中,“if($test$plusargs("FSDB_ON"))”表示从命令行读取参数并判断是否开启波形dump处理。如果去掉这个if判断,就表示无条件的波形dump。当然,正式项目开发中通常会加上条件判断,将开关控制权留到实际做仿真时去。因为回归验证由于要做大量的仿真,通常是不会dump波形,只有单个testcase的调试时才会进行仿真验证。

7.4.1 vcs仿真器

对应于以上代码中的参数名“FSDB_ON”,VCS仿真时在命令行以如下方式指定参数即表示开启FSDB波形dump:

vcs ... +FDDB_ON ...7.4.2 irun仿真器

与vcs的命令行格式略有不同,irun命令行不需要“+” 。如下所示:

irun ... FSDB_ON ...

7.5 Memory Size Limit Problem

在仿真中dump波形经常会碰到如下问题:

*Verdi* FSDB: For performance reasons, the Memory Size Limit has been increased to 512M.

to be investigated.

8. 基本的Makefile例

irun例子:

TB = tb

SEED = 1

run: tb.v

irun -sv +access+rwc -f rtl.f -timescale 1ns/10ps

.PHONY:clean

clean:

rm -rf ./INCA_libs *.log irun.history

vcs例子:

.PHONY:comp sim clean

OUTPUT = adder_top

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \

SIM = ./${OUTPUT} -l run.log

comp:

${VCS} -f verilog_file.f

sim:

${SIM}

clean:

rm -rf ./csrc *.daidir *.log simv* *.key参考文献:

[1] vcs/verdi filist - FLYMOOD - 博客园 (cnblogs.com)

[2] VCS User Guide

[3] Questa SIM User's Manual

智能推荐

vue3背景下,el-input嵌套在弹出框中,自动聚焦“失效”?如何实现自动聚焦_vue3 el-input 自动聚焦autofocus无效-程序员宅基地

文章浏览阅读436次,点赞15次,收藏2次。原因或许是,使用autofocus时,确实聚焦了!但是当我们又点击 显示弹出框的按钮时,input又失焦了,所以当我们看到input框时,没有自动聚焦。_vue3 el-input 自动聚焦autofocus无效

linux网络服务配置说课,《说课稿LINUX》PPT课件.ppt-程序员宅基地

文章浏览阅读222次。《《说课稿LINUX》PPT课件.ppt》由会员分享,可在线阅读,更多相关《《说课稿LINUX》PPT课件.ppt(16页珍藏版)》请在装配图网上搜索。1、LINUX 基础应用与配置管理 桂林山水职业学院计算机系 朱笑雷 主要内容 课程定位 1 课程内容设置 2 教学方法与手段 3 教材建设 4 教学团度 5 主要内容 实践条件 6 课程考核 7 教学效果 8 课程特色 9 建设思路 10 一、课..._linux说课课件

在SpringBoot中启动时关于连接数据库失败的问题_springboot启动时数据库连接失败 不关闭-程序员宅基地

文章浏览阅读2.2k次。#在SpringBoot中启动时关于连接数据库失败的问题对照了application.yml,发现配置文件貌似没什么问题,但是在查找信息之后,发现问题正是出现在application.yml中问题出于datasource下的data-username和data-password只要将data-username和data-password改为username和password即可..._springboot启动时数据库连接失败 不关闭

antd-pro(V5)动态菜单_antdpro的菜单-程序员宅基地

文章浏览阅读4.6k次。一般情况下登录系统后菜单是由后端返回的,不是前端写死的。antd-pro也支持,修改的路径在app.tsx在 layout 里加一个menuDataRender字段先给一个() =>[]可以看到左侧菜单没了,说明配置生效了,接下来就可以围绕这个配置做文章了,我们先定义一个 menuDataRender方法。根据登录缓存到本地的数据做下处理,判断菜单里要展示哪些内容(比如替换字段,隐藏不显示的菜单,隐藏按钮等),处理好了后返回一个数组结构即可。示例代码如下export const layout: _antdpro的菜单

Linux安装使用jprofiler6分析服务器应用状态-程序员宅基地

文章浏览阅读77次。为什么80%的码农都做不了架构师?>>> ..._jprofiler6 key

苏小红C语言第四版课后习题练习7.7最大公约数三种计算方式_c语言程序设计第四版课后题答案苏小红第七章-程序员宅基地

文章浏览阅读170次。(可以看出递归算法更加侧重于计算的技巧,并且计算机计算的次数也相对更少);_c语言程序设计第四版课后题答案苏小红第七章

随便推点

Fiddler抓包,并修改请求数据_filder改数据包-程序员宅基地

文章浏览阅读4.4w次,点赞8次,收藏51次。浏览器抓包(工具:fiddler)并 修改请求内容 工具下载:https://pan.baidu.com/s/1pyKdAwgTdNNvoWA2bGlk9A 1、正常打开网页,输入要提交的内容 2、打开工具,f11暂停了页面的所有提交动作 3、这时再点击提交按钮,请求的数据就会被工具拦截 4、双击截取的数据,右侧会看到请求的具体内容,任意修改数据 5、点击绿色按钮 run ..._filder改数据包

视频格式转换器榜单:10 款最值得拥有的高清视频转换器_奇客视频转换-程序员宅基地

文章浏览阅读560次。如果您想在计算机或任何其他设备上播放高质量的视频,高清视频转换器可以帮助确保您的视频与您的操作系统和硬件兼容。您还可以使用高清转换器更改视频的分辨率,无论您是想提高质量还是降低分辨率以生成更小的文件。在下表中,我们描述了用于转换高清视频的最流行和可用的桌面程序和在线服务。它们各有优缺点,因此请根据您的需要进行选择。_奇客视频转换

Unity血条效果,图片动画_游戏血条动图-程序员宅基地

文章浏览阅读1.9k次。欢迎来到unity学习、unity培训、unity企业培训教育专区,这里有很多U3D资源、U3D培训视频,我们致力于打造业内unity3d培训、学习第一品牌。今天开始做我们的游戏了,组长给分配了任务,我负责做剧情动画,人物血条和种植植物。 一、剧情动画 动画是以多个图片的形式展现的,图片是自己制作的。 private GUITextu_游戏血条动图

环境变量的加载顺序、环境变量集合_环境变量的顺序-程序员宅基地

文章浏览阅读1k次。*******字符编码ASCII,GB2312,GBK,Unicode,UTF-8比较参考:https://blog.csdn.net/softwarenb/article/details/51994943**环境变量的加载顺序:Mac系统的环境变量,加载顺序为:a. /etc/profileb. /etc/pathsc. ~/.bash_profiled. ~/..._环境变量的顺序

科学家发现让人类幸福感飙升的密码!给大脑植入这个算法 | 精选-程序员宅基地

文章浏览阅读316次。▼大型年度AI人物评选——2017中国AI英雄风云榜已于12月4日在乌镇张榜,12月18日在北京国贸三期举行颁奖典礼。榜单评选出年度技术创新人物TOP 10;商业创新人物TOP 10,获取完整榜单请关注网易智能公众号(ID:smartman163),回复关键词“评奖”。本文系网易智能工作室出品聚焦AI,读懂下一个大时代【网易智能讯12月10日消息】不只有你会_人类大脑植入代码

正则表达式匹配中括号内的内容_正则<>里内容-程序员宅基地

文章浏览阅读3.6k次。几经研究, 终于实现了。time[2020-06-04 11:43:36](?<=\[)(.*)(?=])(pattern) 匹配 pattern 并获取这一匹配。所获取的匹配可以从产生的 Matches 集合得到,在VBScript 中使用 SubMatches 集合,在JScript 中则使用 $0…$9 属性。要匹配圆括号字符,请使用 '\(' 或 '\)'。 (?:pattern) 匹配 pattern 但不获取匹配结..._正则<>里内容