Verilog CIC 滤波器设计(代码自取)_cic截止频率-程序员宅基地

前言:积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器,资源消耗少,运算速率高,可实现高速滤波,常用在输入采样率最高的第一级,在多速率信号处理系统中具有着广泛应用。

1. DDC 原理

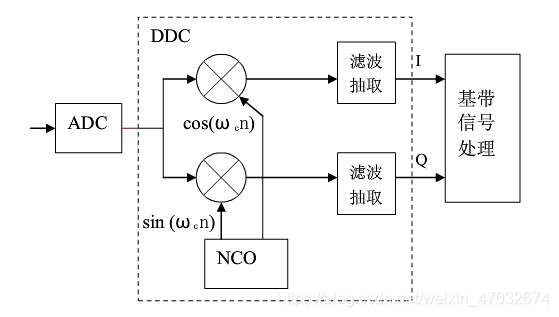

DDC 主要由本地振荡器(NCO) 、混频器、滤波器等组成,如下图所示。

DDC 将中频信号与振荡器产生的载波信号进行混频,信号中心频率被搬移,再经过抽取滤波,恢复原始信号,实现了下变频功能。

中频数据采样时,需要很高的采样频率来确保 ADC(模数转换器)采集到信号的信噪比。经过数字下变频后,得到的基带信号采样频率仍然是 ADC 采样频率,所以数据率很高。此时基带信号的有效带宽往往已经远小于采样频率,所以利用抽取、滤波进行数据速率的转换,使采样率降低,避免资源的浪费和设计的困难,就成为 DDC 不可缺少的一部分。

而采用 CIC 滤波器进行数据处理,是 DDC 抽取滤波部分最常用的方法。

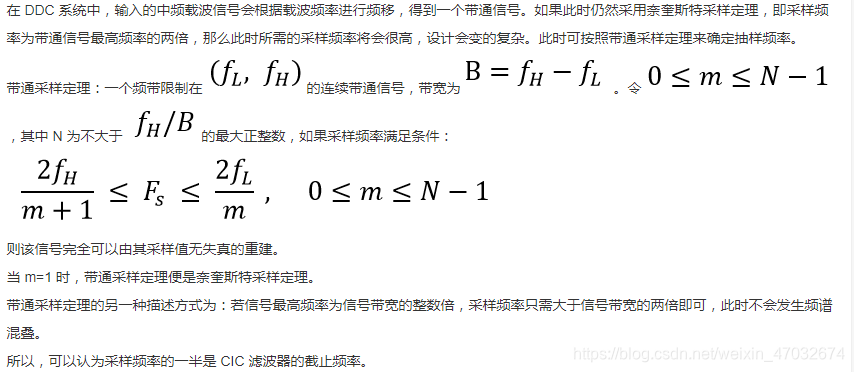

2.带通采样定理

3. DDC 频谱搬移

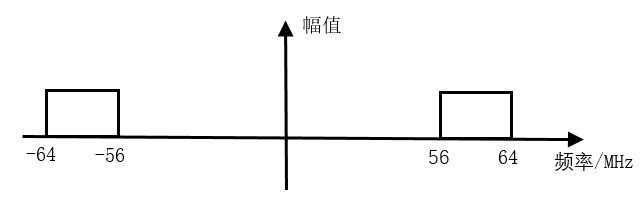

例如一个带宽信号中心频率为 60MHz,带宽为 8MHz, 则频率范围为 56MHz ~ 64MHz,m 的可取值范围为 0 ~ 7。取 m=1, 则采样频率范围为 64MHz ~ 112MHz。

取采样频率为 80MHz,设 NCO 中心频率为 20 MHz,下面讨论复信号频谱搬移示意图。

(1)考虑频谱的对称性,输入复信号的频谱示意图如下:

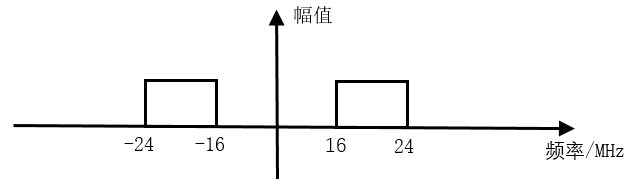

(2)80MHz 采样频率采样后,56~64MHz 的频带被搬移到了 -24~ -16MHz 与 136 ~ 144MHz(高于采样频率被滤除)的频带处,-64~ -56MHz 的频带被搬移到 -144~ -136MHz(高于采样频率被滤除)与 16~24MHz 的频带处。

采样后频带分布如下:

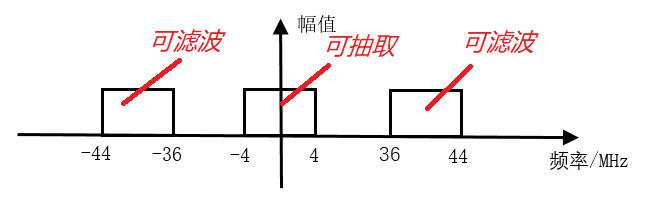

(3)信号经过 20MHz NCO 的正交电路后, -24~ -16MHz 的频带被搬移到 -4~4MHz 与 -44~ -36MHz 的频带处,16~24MHz 的频带被搬移到 -4~4MHz 与 36~44MHz 的频带处,如下所示。

(4)此时中频输入的信号已经被搬移到零中频基带处。

-44~ -36MHz 和 36~44MHz 的带宽信号是不需要的,可以滤除;-4~4MHz 的零中频信号数据速率仍然是 80MHz,可以进行抽取降低数据速率。而 CIC 滤波,就是要完成这个过程。

上述复习了很多数字信号处理的内容,权当抛 DDC 的砖,引 CIC 的玉。

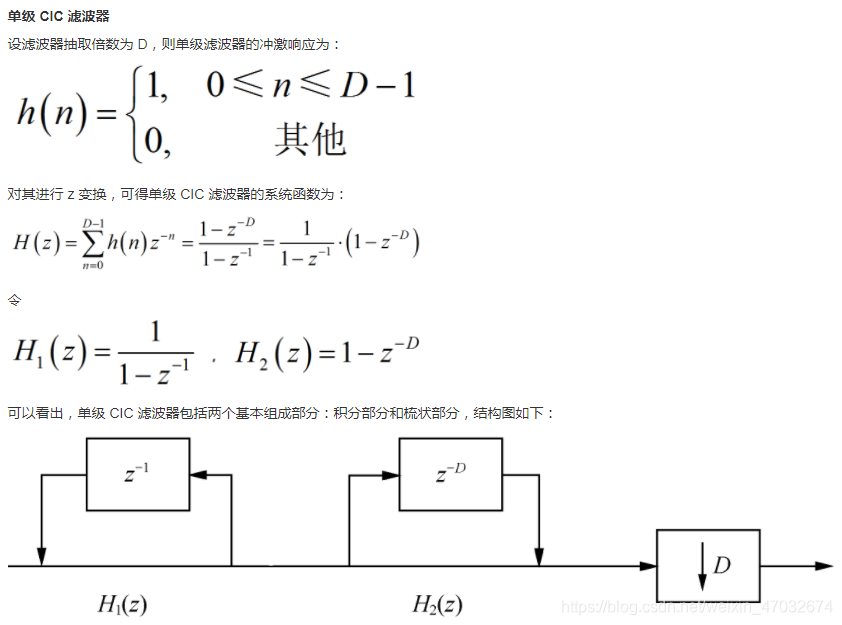

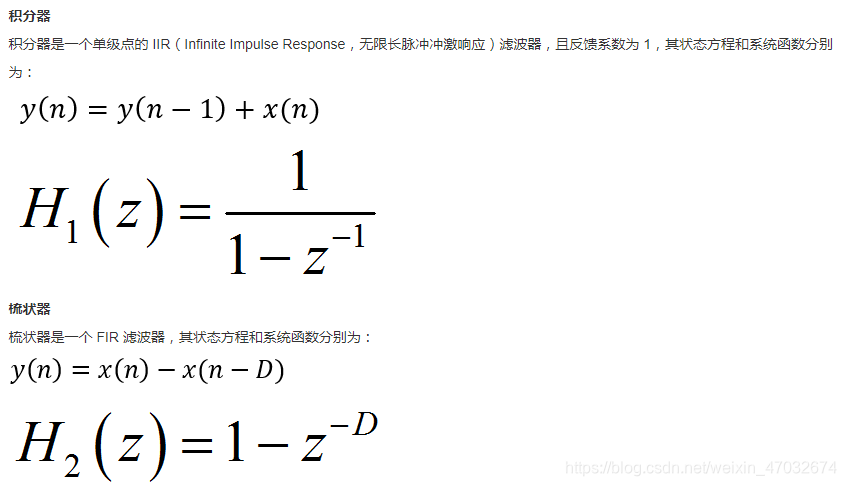

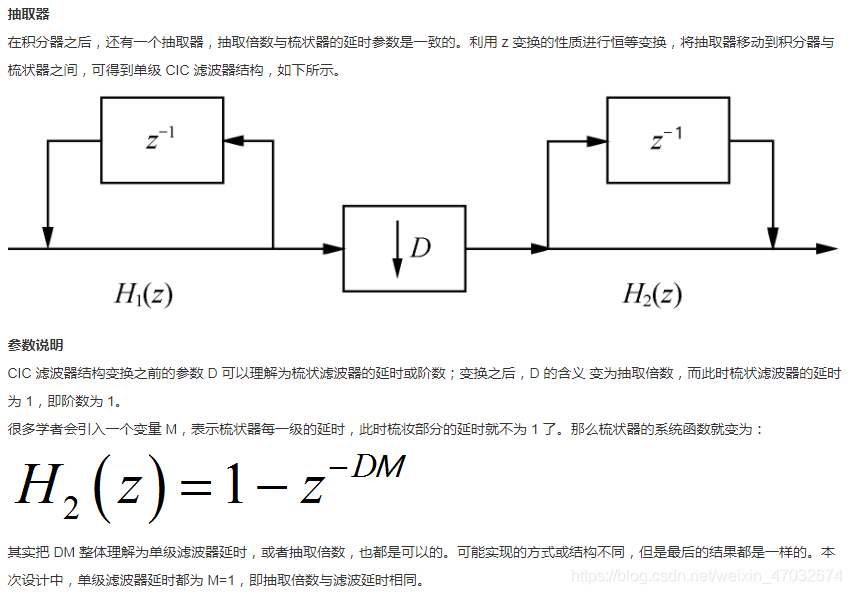

4.CIC 滤波器原理

多级 CIC 滤波器

单级 CIC 滤波器的阻带衰减较差,为了提高滤波效果,抽取滤波时往往会采用多级 CIC 滤波器级联的结构。

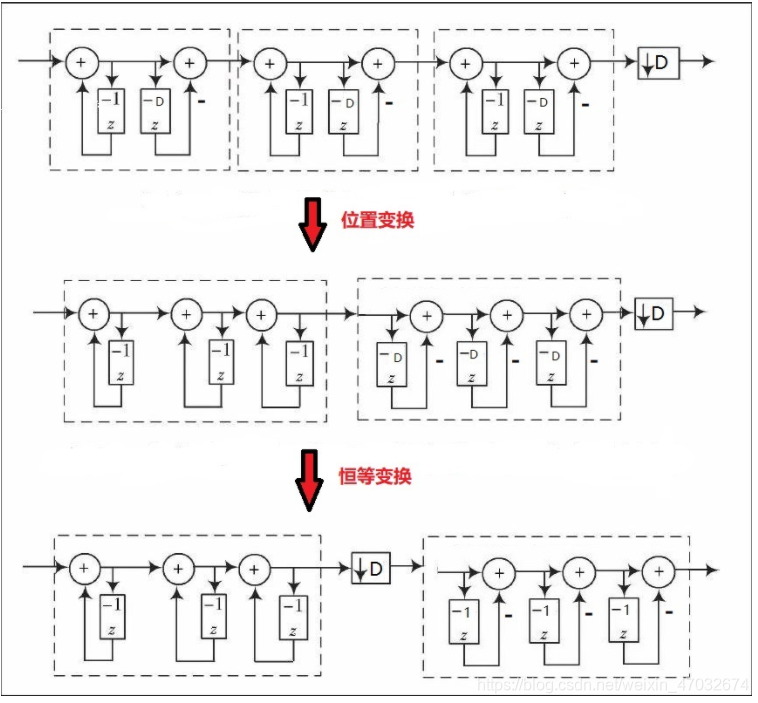

实现多级直接级联的 CIC 滤波器在设计和资源上并不是最优的方式,需要对其结构进行调整。如下所示,将积分器和梳状滤波器分别移至一组,并将抽取器移到梳状滤波器之前。先抽取再进行滤波,可以减少数据处理的长度,节约硬件资源。

当然,级联数越大,旁瓣抑制越好,但是通带内的平坦度也会变差。所以级联数不宜过多,一般最多 5 级。

5.CIC 滤波器设计

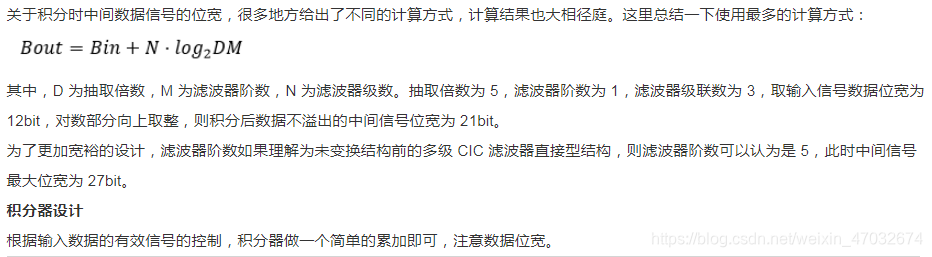

设计说明

CIC 滤波器本质上就是一个简单的低通滤波器,截止频率为采样频率除以抽取倍数后的一半。输入数据信号仍然是 7.5MHz 和 250KHz,采样频率 50MHz。抽取倍数设置为 5,则截止频率为 5MHz,小于 7.5MHz,可以滤除 7.5MHz 的频率成分。设计参数如下:

输入频率: 7.5MHz 和 250KHz

采样频率: 50MHz

阻带: 5MHz

阶数: 1(M=1)

级数: 3(N=3)

//3 stages integrator

module integrator

#(parameter NIN = 12,

parameter NOUT = 21)

(

input clk ,

input rstn ,

input en ,

input [NIN-1:0] din ,

output valid ,

output [NOUT-1:0] dout) ;

reg [NOUT-1:0] int_d0 ;

reg [NOUT-1:0] int_d1 ;

reg [NOUT-1:0] int_d2 ;

wire [NOUT-1:0] sxtx = {

{(NOUT-NIN){1'b0}}, din} ;

//data input enable delay

reg [2:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else begin

en_r <= {en_r[1:0], en};

end

end

//integrator

//stage1

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d0 <= 'b0 ;

end

else if (en) begin

int_d0 <= int_d0 + sxtx ;

end

end

//stage2

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d1 <= 'b0 ;

end

else if (en_r[0]) begin

int_d1 <= int_d1 + int_d0 ;

end

end

//stage3

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

int_d2 <= 'b0 ;

end

else if (en_r[1]) begin

int_d2 <= int_d2 + int_d1 ;

end

end

assign dout = int_d2 ;

assign valid = en_r[2];

endmodule

抽取器设计

抽取器设计时,对积分器输出的数据进行计数,然后间隔 5 个数据进行抽取即可。

module decimation

#(parameter NDEC = 21)

(

input clk,

input rstn,

input en,

input [NDEC-1:0] din,

output valid,

output [NDEC-1:0] dout);

reg valid_r ;

reg [2:0] cnt ;

reg [NDEC-1:0] dout_r ;

//counter

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 3'b0;

end

else if (en) begin

if (cnt==4) begin

cnt <= 'b0 ;

end

else begin

cnt <= cnt + 1'b1 ;

end

end

end

//data, valid

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

valid_r <= 1'b0 ;

dout_r <= 'b0 ;

end

else if (en) begin

if (cnt==4) begin

valid_r <= 1'b1 ;

dout_r <= din;

end

else begin

valid_r <= 1'b0 ;

end

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

梳状器设计

梳状滤波器就是简单的一阶 FIR 滤波器,每一级的 FIR 滤波器对数据进行一个时钟延时,然后做相减即可。因为系数为 ±1,所以不需要乘法器。

module comb

#(parameter NIN = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

//en delay

reg [5:0] en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

en_r <= 'b0 ;

end

else if (en) begin

en_r <= {en_r[5:0], en} ;

end

end

reg [NOUT-1:0] d1, d1_d, d2, d2_d, d3, d3_d ;

//stage 1, as fir filter, shift and add(sub),

//no need for multiplier

always @(posedge clk or negedge rstn) begin

if (!rstn) d1 <= 'b0 ;

else if (en) d1 <= din ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d1_d <= 'b0 ;

else if (en) d1_d <= d1 ;

end

wire [NOUT-1:0] s1_out = d1 - d1_d ;

//stage 2

always @(posedge clk or negedge rstn) begin

if (!rstn) d2 <= 'b0 ;

else if (en) d2 <= s1_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d2_d <= 'b0 ;

else if (en) d2_d <= d2 ;

end

wire [NOUT-1:0] s2_out = d2 - d2_d ;

//stage 3

always @(posedge clk or negedge rstn) begin

if (!rstn) d3 <= 'b0 ;

else if (en) d3 <= s2_out ;

end

always @(posedge clk or negedge rstn) begin

if (!rstn) d3_d <= 'b0 ;

else if (en) d3_d <= d3 ;

end

wire [NOUT-1:0] s3_out = d3 - d3_d ;

//tap the output data for better display

reg [NOUT-1:0] dout_r ;

reg valid_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

dout_r <= 'b0 ;

valid_r <= 'b0 ;

end

else if (en) begin

dout_r <= s3_out ;

valid_r <= 1'b1 ;

end

else begin

valid_r <= 1'b0 ;

end

end

assign dout = dout_r ;

assign valid = valid_r ;

endmodule

顶层例化

按信号的流向将积分器、抽取器、梳状器分别例化,即可组成最后的 CIC 滤波器模块。

梳状滤波器的最终输出位宽一般会比输入信号小一些,这里取 17bit。当然输出位宽完全可以与输入数据的位宽一致。

module cic

#(parameter NIN = 12,

parameter NMAX = 21,

parameter NOUT = 17)

(

input clk,

input rstn,

input en,

input [NIN-1:0] din,

input valid,

output [NOUT-1:0] dout);

wire [NMAX-1:0] itg_out ;

wire [NMAX-1:0] dec_out ;

wire [1:0] en_r ;

integrator #(.NIN(NIN), .NOUT(NMAX))

u_integrator (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (en_r[0]),

.dout (itg_out));

decimation #(.NDEC(NMAX))

u_decimator (

.clk (clk),

.rstn (rstn),

.en (en_r[0]),

.din (itg_out),

.dout (dec_out),

.valid (en_r[1]));

comb #(.NIN(NMAX), .NOUT(NOUT))

u_comb (

.clk (clk),

.rstn (rstn),

.en (en_r[1]),

.din (dec_out),

.valid (valid),

.dout (dout));

endmodule

testbench

testbench 编写如下,主要功能就是不间断连续的输入 250KHz 与 7.5MHz 的正弦波混合信号数据。输入的混合信号数据也可由 matlab 生成,具体过程参考《并行 FIR 滤波器设计》一节。

module test ;

parameter NIN = 12 ;

parameter NMAX = 21 ;

parameter NOUT = NMAX ;

reg clk ;

reg rstn ;

reg en ;

reg [NIN-1:0] din ;

wire valid ;

wire [NOUT-1:0] dout ;

//=====================================

// 50MHz clk generating

localparam T50M_HALF = 10000;

initial begin

clk = 1'b0 ;

forever begin

# T50M_HALF clk = ~clk ;

end

end

//============================

// reset and finish

initial begin

rstn = 1'b0 ;

# 30 ;

rstn = 1'b1 ;

# (T50M_HALF * 2 * 2000) ;

$finish ;

end

//=======================================

// read cos data into register

parameter SIN_DATA_NUM = 200 ;

reg [NIN-1:0] stimulus [0: SIN_DATA_NUM-1] ;

integer i ;

initial begin

$readmemh("../tb/cosx0p25m7p5m12bit.txt", stimulus) ;

i = 0 ;

en = 0 ;

din = 0 ;

# 200 ;

forever begin

@(negedge clk) begin

en = 1 ;

din = stimulus[i] ;

if (i == SIN_DATA_NUM-1) begin

i = 0 ;

end

else begin

i = i + 1 ;

end

end

end

end

cic #(.NIN(NIN), .NMAX(NMAX), .NOUT(NOUT))

u_cic (

.clk (clk),

.rstn (rstn),

.en (en),

.din (din),

.valid (valid),

.dout (dout));

endmodule // test

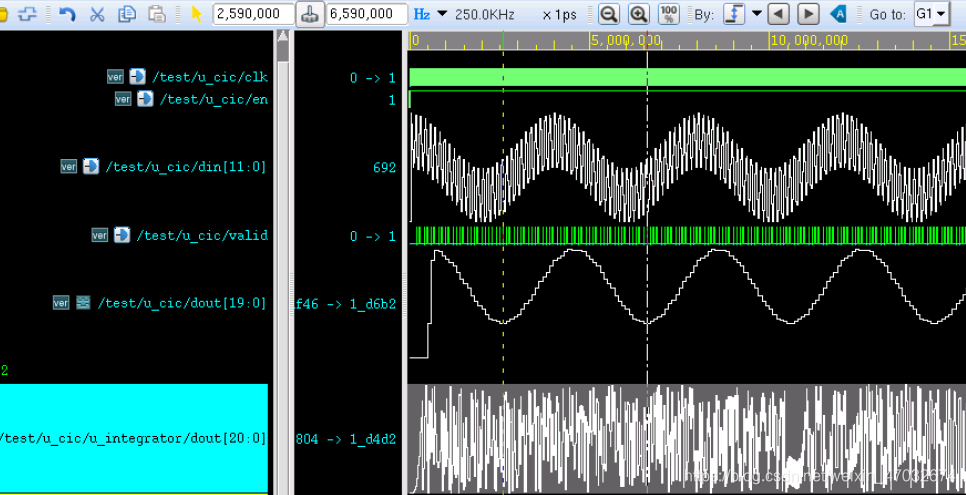

6.仿真结果

由下图仿真结果可知,经过 CIC 滤波器后的信号只有一种低频率信号(250KHz),高频信号(7.5MHz)被滤除了。

但是波形不是非常完美,这与设计的截止频率、数据不是持续输出等有一定关系。

此时发现,积分器输出的数据信号也非常的不规则,这与其位宽有关系。

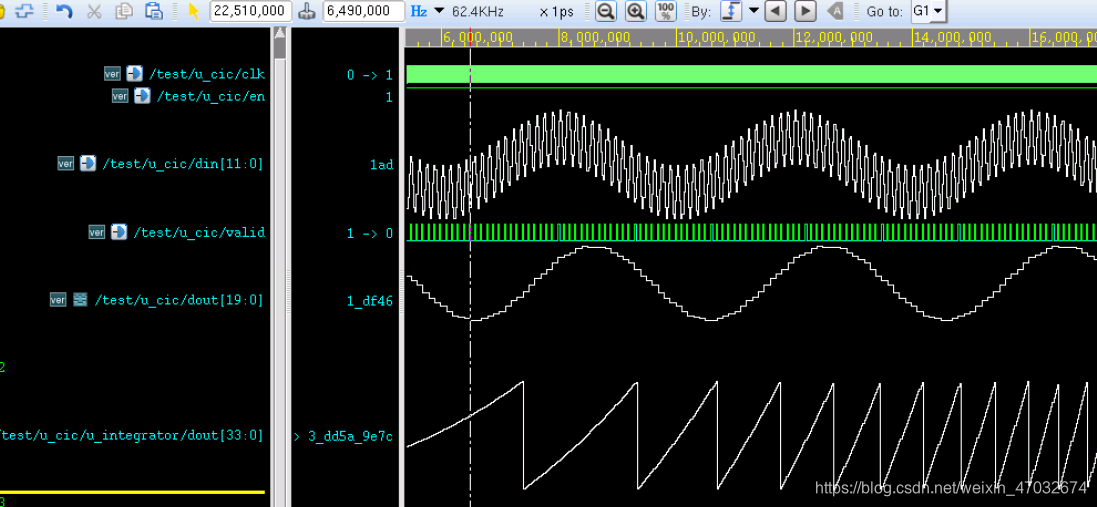

为了更好的观察积分器输出的数据,将其位宽由 21bit 改为 34bit,仿真结果如下。

此时发现,CIC 滤波器的数据输出并没有实质性的变化,但是积分器输出的数据信号呈现锯齿状,也称之为梳状。这也是梳状滤波器名字的由来。

智能推荐

计算机丢失concrt140,小编教你解决concrt140 dll 【解决教程】 的技巧_-程序员宅基地

文章浏览阅读4.5w次。近日有小伙伴发现电脑出现问题了,在突然遇到concrt140 dll时不知所措了,对于concrt140 dll带来的问题,其实很好解决concrt140 dll带来的问题,下面小编跟大家介绍concrt140 dll解决方法:丢失CONCRT140.dll,怎么办?答:分析及解决:网上下载这个DLL文件,将其放置到system32目录下面。 重启系统,或者在CMD下面运行regsvr32*.dl..._concrt140.dll下载教程

微信小程序源码案例大全_微信小程序switch页面demo-程序员宅基地

文章浏览阅读4.3k次,点赞4次,收藏62次。微信小程序demo:足球,赛事分析 小程序简易导航 小程序demo:办公审批 小程序Demo:电魔方 小程序demo:借阅伴侣 微信小程序demo:投票 微信小程序demo:健康生活 小程序demo:文章列表demo 微商城(含微信小程序)完整源码+配置指南 微信小程序Demo:一个简单的工作系统 微信小程序Demo:用于聚会的小程序 微信小程序Demo:Growth 是一款..._微信小程序switch页面demo

SLAM学习笔记(Code2)----刚体运动、Eigen库_eigen.determinant-程序员宅基地

文章浏览阅读2.2k次。2.1除了#include<iostream>之外的头文件#include <Eigen/Core>//Core:核心#include <Eigen/Dense>//求矩阵的逆、特征值、行列式等#include <Eigen/Geometry>//Eigen的几何模块,可以利用矩阵完成如旋转、平移/***其他***/#include <ctime>//可用于计时,比较哪个程序更快#include <cmath>//包含a_eigen.determinant

图像梯度-sobel算子-程序员宅基地

文章浏览阅读1w次,点赞12次,收藏61次。(1)理论部分x 水平方向的梯度, 其实也就是右边 - 左边,有的权重为1,有的为2 。若是计算出来的值很大 说明是一个边界 。y 竖直方向的梯度,其实也就是下面减上面,权重1,或2 。若是计算出来的值很大 说明是一个边界 。图像的梯度为:有时简化为:即:(2)程序部分函数:Sobelddepth 通常取 -1,但是会导致结果溢出,检测不出边缘,故使..._sobel算子

cuda10.1和cudnn7.6.5百度网盘下载链接(Linux版)_cudnn7.6网盘下载-程序员宅基地

文章浏览阅读3.6k次,点赞17次,收藏8次。cuda10.1和cudnn7.6.5百度网盘下载链接(Linux版)在官网下载不仅慢,,,主要是还总失败。。终于下载成功了,这里给出百度网盘下载链接,希望可以帮到别人百度网盘下载链接提取码: vyg5_cudnn7.6网盘下载

Python正则表达式大全-程序员宅基地

文章浏览阅读9.3w次,点赞69次,收藏427次。定义:正则表达式是对字符串(包括普通字符(例如,a 到 z 之间的字母)和特殊字符(称为“元字符”))操作的一种逻辑公式,就是用事先定义好的一些特定字符、及这些特定字符的组合,组成一个“规则字符串”,这个“规则字符串”用来表达对字符串的一种过滤逻辑。正则表达式是一种文本模式,该模式描述在搜索文本时要匹配的一个或多个字符串。上面都是官方的说明,我自己的理解是(仅供参考):通过事先规定好一些特殊字符的匹配规则,然后利用这些字符进行组合来匹配各种复杂的字符串场景。比如现在的爬虫和数据分析,字符串校验等等都需要用_python正则表达式

随便推点

NILM(非侵入式电力负荷监测)学习笔记 —— 准备工作(一)配置环境NILMTK Toolkit_nilmtk学习-程序员宅基地

文章浏览阅读1.9w次,点赞27次,收藏122次。安装Anaconda,Python,pycharm我另一篇文章里面有介绍https://blog.csdn.net/wwb1990/article/details/103883775安装NILMTK有了上面的环境,接下来进入正题。NILMTK官网:http://nilmtk.github.io/因为官方安装流程是基于linux的(官方安装流程),我这里提供windows..._nilmtk学习

k8s-pod 控制器-程序员宅基地

文章浏览阅读826次,点赞20次,收藏28次。如果实际 Pod 数量比指定的多那就结束掉多余的,如果实际数量比指定的少就新启动一些Pod,当 Pod 失败、被删除或者挂掉后,RC 都会去自动创建新的 Pod 来保证副本数量,所以即使只有一个 Pod,我们也应该使用 RC 来管理我们的 Pod。label 与 selector 配合,可以实现对象的“关联”,“Pod 控制器” 与 Pod 是相关联的 —— “Pod 控制器”依赖于 Pod,可以给 Pod 设置 label,然后给“控制器”设置对应的 selector,这就实现了对象的关联。

相关工具设置-程序员宅基地

文章浏览阅读57次。1. ultraEdit设置禁止自动更新: 菜单栏:高级->配置->应用程序布局->其他 取消勾选“自动检查更新”2.xshell 传输文件中设置编码,防止乱码: 文件 -- 属性 -- 选项 -- 连接 -- 使用UTF-8编码3.乱码修改:修改tomcat下配置中,修改: <Connector connectionTimeou..._高级-配置-应用程序布局

ico引入方法_arco的ico怎么导入-程序员宅基地

文章浏览阅读1.2k次。打开下面的网站后,挑选要使用的,https://icomoon.io/app/#/select/image下载后 解压 ,先把fonts里面的文件复制到项目fonts文件夹中去,然后打开其中的style.css文件找到类似下面的代码@font-face {font-family: ‘icomoon’;src: url(’…/fonts/icomoon.eot?r069d6’);s..._arco的ico怎么导入

Microsoft Visual Studio 2010(VS2010)正式版 CDKEY_visual_studio_2010_professional key-程序员宅基地

文章浏览阅读1.9k次。Microsoft Visual Studio 2010(VS2010)正式版 CDKEY / SN:YCFHQ-9DWCY-DKV88-T2TMH-G7BHP企业版、旗舰版都适用推荐直接下载电驴资源的vs旗舰版然后安装,好用方便且省时!) MSDN VS2010 Ultimate 简体中文正式旗舰版破解版下载(附序列号) visual studio 2010正_visual_studio_2010_professional key

互联网医疗的定义及架构-程序员宅基地

文章浏览阅读3.2k次,点赞2次,收藏17次。导读:互联网医疗是指综合利用大数据、云计算等信息技术使得传统医疗产业与互联网、物联网、人工智能等技术应用紧密集合,形成诊前咨询、诊中诊疗、诊后康复保健、慢性病管理、健康预防等大健康生态深度..._线上医疗的定义