FPGA常见问题解决方法_drc mdrv-1-程序员宅基地

FPGA常见问题解决方法

- 0 使用加法,注意数据位宽的变化

- 1 IP怎么调用

- 2 如何在仿真中观察更多的信号

- 3 仿真波形如何显示十进制数

- 4 常见快捷键

- 6 约束文件的两种方法

- 7 修改源文件或者约束文件或者BD后,发现ILa波形不变如何处理

- 8 xpm_fifo如何使用

- 9 什么时候用input、output;什么时候用wire。两者的区别是什么?

- 10 module 'xpm_fifo_async' not found

- 11 注意点

- 12 [DRC MDRV-1] 多驱动网络

- 13 自己封装的IP如何保证每次修改IP后,不会影响以前工程的IP。

- 14 光标变成黑块解决方法

- 15 testbench文件的报错如何找到错误详细信息

- 16 Vivado IP核锁定的解决办法(两种解决办法)

0 使用加法,注意数据位宽的变化

// 将四个阵元加权后的信号合成起来

//下面这行代码不对,没有考虑位宽的扩展

//assign real_y = Ct_1I+Ct_2I+Ct_3I+Ct_4I; // 实部

// 为什么需要扩展两位

// 比如:4个1相加等于4,加数只需要1bit进行表示,而和需要3bit进行表示,所以要扩展两位

// 由于最后只需要16bit,所以低两位不要。

wire [17:0] real_y_18bit;

wire [17:0] imag_y_18bit;

assign real_y_18bit = {

Ct_1I[15],Ct_1I[15],Ct_1I}

+{

Ct_2I[15],Ct_2I[15],Ct_2I}

+{

Ct_3I[15],Ct_3I[15],Ct_3I}

+{

Ct_4I[15],Ct_4I[15],Ct_4I}; // 实部

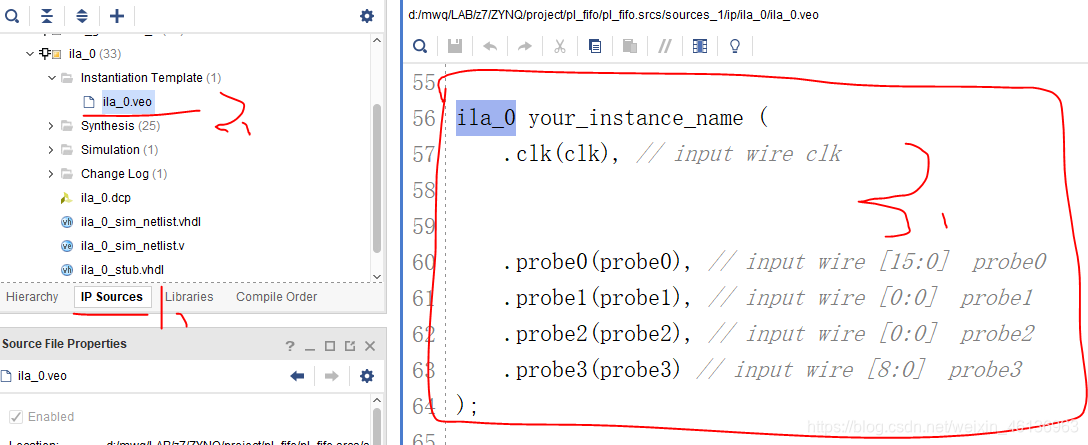

1 IP怎么调用

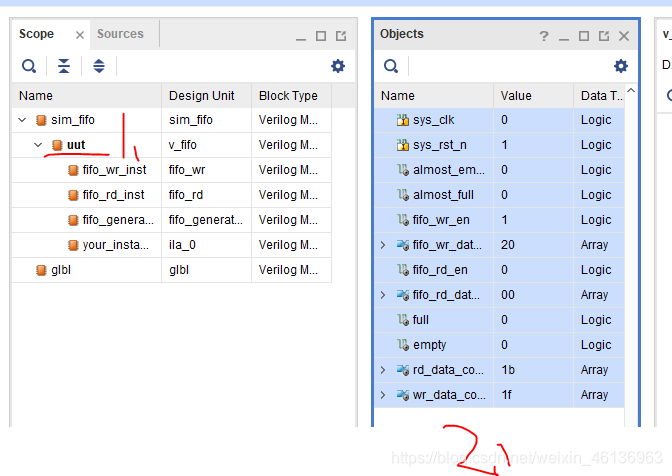

2 如何在仿真中观察更多的信号

跑出结果后—双击uut----选中object的所有信号—右键,点击 add to wave window

3 仿真波形如何显示十进制数

点击信号---------右键,点击radix--------点击 unsigned dec

4 常见快捷键

批量修改快捷键:Ctrl+Alt

6 约束文件的两种方法

法一:点击“Open Elaborated Design”------在弹出的窗口中点击“OK”按钮----------------在菜单中选择“Window -> I/O Ports”-----------在弹出的 I/O Ports 中可以看到管脚分配情况

法二:新建约束文件-----编写约束文件

7 修改源文件或者约束文件或者BD后,发现ILa波形不变如何处理

(1)检查是否export硬件,检查导出硬件时是否勾选了比特流文件。

(2)如果生成比特流文件所花时间较短,则重新生成比特流文件。

(3)关闭软件,重新启动。

(4)重新启动SDK端,并且选择debug界面。

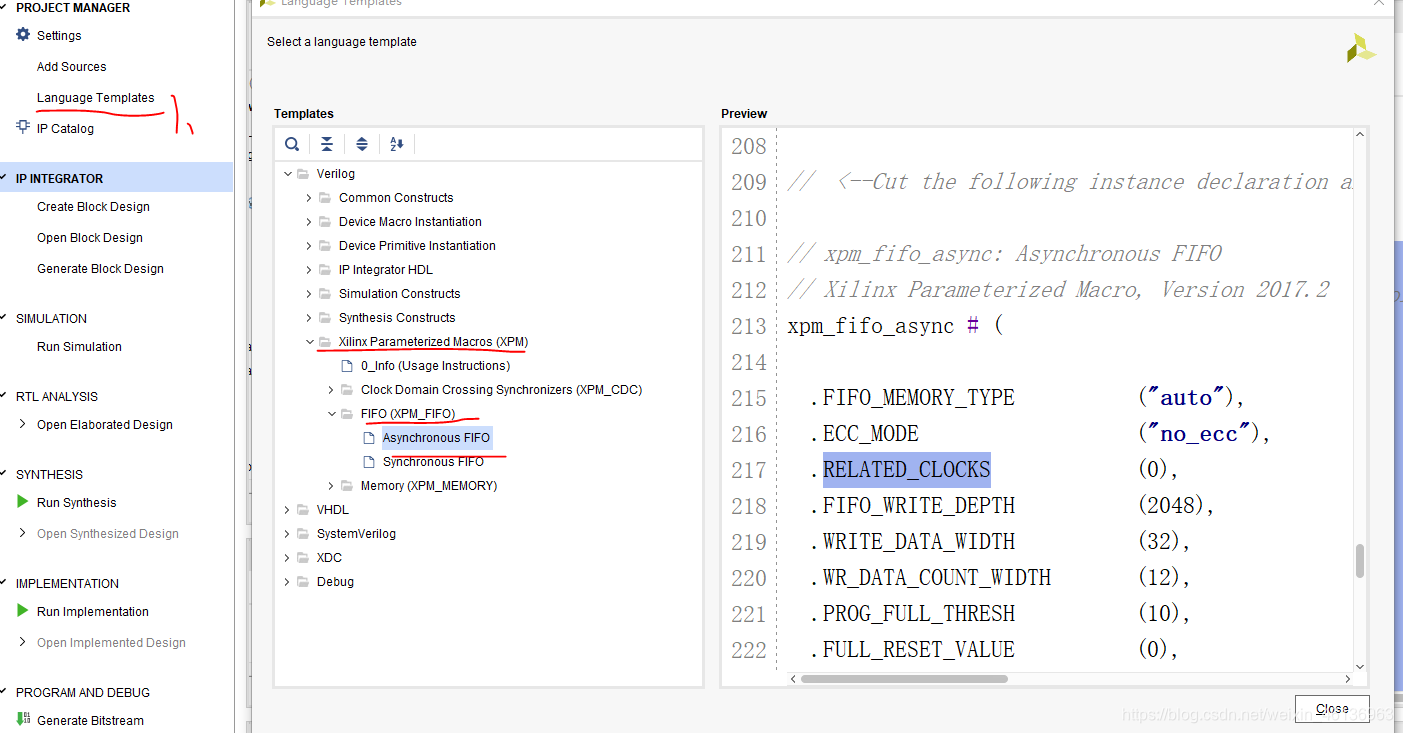

8 xpm_fifo如何使用

Language Templates--------- Verilog-----------Xilinx Parameterized Macros(XPM)--------XPM--------XPM_fifo-----------Asynchronous FIFO,复制到.v中,如下图所示

/*

* Instantiate async fifo by using Xilinx parameterized Macros. For ultrasclae, refer to ug974, for 7 series ug953

* write and read depth is 1024, write and read data width is 8

*/

xpm_fifo_async #(

.CDC_SYNC_STAGES (2),

.DOUT_RESET_VALUE ("1"),

.ECC_MODE ("no_ecc"),

.FIFO_MEMORY_TYPE ("auto"),

.FIFO_READ_LATENCY (1),

.FIFO_WRITE_DEPTH (1024),

.FULL_RESET_VALUE (0),

.PROG_EMPTY_THRESH (10),

.PROG_FULL_THRESH (10),

.RD_DATA_COUNT_WIDTH (11),

.READ_DATA_WIDTH (8),

.READ_MODE ("std"),

.RELATED_CLOCKS (0),

.USE_ADV_FEATURES ("0707"),

.WAKEUP_TIME (0),

.WRITE_DATA_WIDTH (8),

.WR_DATA_COUNT_WIDTH (11)

)

xpm_fifo_async_inst (

.rst (~adc_rst_n),

.wr_clk (adc_clk),

.wr_en (adc_buf_wr),

.din (adc_buf_data),

.rd_clk (M_AXIS_CLK),

.rd_en (adc_buf_rd),

.dout (M_AXIS_tdata),

.empty (empty),

.full (),

.almost_empty (),

.almost_full (),

.wr_data_count (),

.rd_data_count (),

.prog_empty (),

.prog_full (),

.data_valid (),

.dbiterr (),

.sbiterr (),

.overflow (),

.underflow (),

.wr_ack (),

.wr_rst_busy (),

.rd_rst_busy (),

.injectdbiterr (1'b0),

.injectsbiterr (1'b0),

.sleep (1'b0)

);

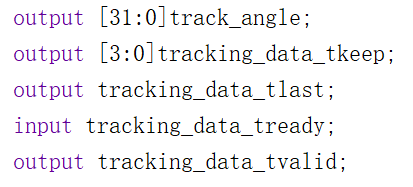

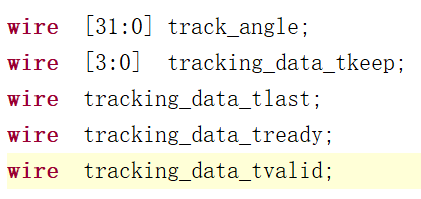

9 什么时候用input、output;什么时候用wire。两者的区别是什么?

第一种情况:用input、output。

用input、output需要编写这5个信号的约束文件。

第二种情况:wire。

此时不需要编写这5个信号的约束文件。

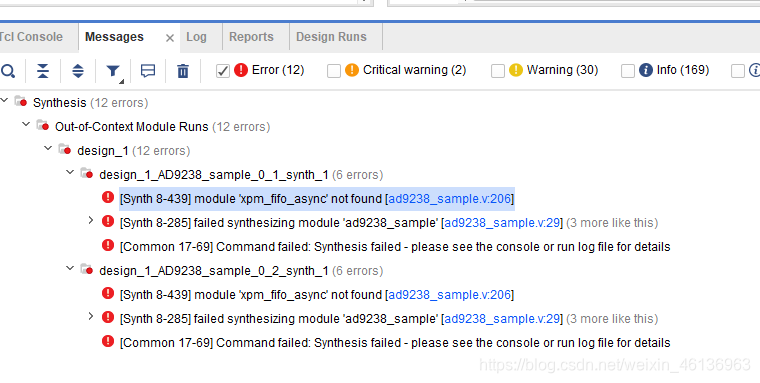

10 module ‘xpm_fifo_async’ not found

解决方法:

在TCL console输入命令:

set_property XPM_LIBRARIES XPM_FIFO [current_project]

11 注意点

(1)“Run As”时最好勾选复位,以及program 比特流文件。

(2)有 PL 的设计要“Program FPGA”,如果PL 多次修改,别忘了重新导出硬件。

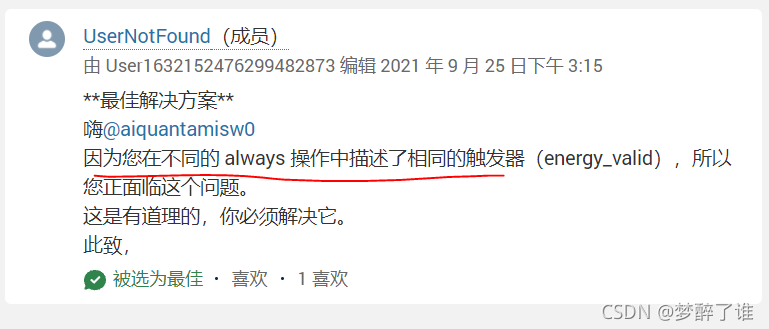

12 [DRC MDRV-1] 多驱动网络

13 自己封装的IP如何保证每次修改IP后,不会影响以前工程的IP。

(1)将IP封装好后,命名为repo。

(2)每建立一个工程文件时,将repo文件复制在该工程目录下。

(3)打开该工程,注意删除以前的IP repo文件,重新添加本工程文件目录下的IP repo.

14 光标变成黑块解决方法

按一下 insert即可

15 testbench文件的报错如何找到错误详细信息

打开.sim文件,\sim_1\behav目录下

16 Vivado IP核锁定的解决办法(两种解决办法)

法一:

1.生成IP核的状态报告 Tools -> Report -> Report IP Status

2.点击Upgrade Selected

3.更新完成后IP Status

法二:

下面介绍另一种方法,对应上述方法不能使用的情况(Upgrade Selected 按钮是灰色的 情况)

在 Tcl console中 执行如下一条命令即可:

upgrade_ip [get_ips]

智能推荐

攻防世界_难度8_happy_puzzle_攻防世界困难模式攻略图文-程序员宅基地

文章浏览阅读645次。这个肯定是末尾的IDAT了,因为IDAT必须要满了才会开始一下个IDAT,这个明显就是末尾的IDAT了。,对应下面的create_head()代码。,对应下面的create_tail()代码。不要考虑爆破,我已经试了一下,太多情况了。题目来源:UNCTF。_攻防世界困难模式攻略图文

达梦数据库的导出(备份)、导入_达梦数据库导入导出-程序员宅基地

文章浏览阅读2.9k次,点赞3次,收藏10次。偶尔会用到,记录、分享。1. 数据库导出1.1 切换到dmdba用户su - dmdba1.2 进入达梦数据库安装路径的bin目录,执行导库操作 导出语句:./dexp cwy_init/[email protected]:5236 file=cwy_init.dmp log=cwy_init_exp.log 注释: cwy_init/init_123..._达梦数据库导入导出

js引入kindeditor富文本编辑器的使用_kindeditor.js-程序员宅基地

文章浏览阅读1.9k次。1. 在官网上下载KindEditor文件,可以删掉不需要要到的jsp,asp,asp.net和php文件夹。接着把文件夹放到项目文件目录下。2. 修改html文件,在页面引入js文件:<script type="text/javascript" src="./kindeditor/kindeditor-all.js"></script><script type="text/javascript" src="./kindeditor/lang/zh-CN.js"_kindeditor.js

STM32学习过程记录11——基于STM32G431CBU6硬件SPI+DMA的高效WS2812B控制方法-程序员宅基地

文章浏览阅读2.3k次,点赞6次,收藏14次。SPI的详情简介不必赘述。假设我们通过SPI发送0xAA,我们的数据线就会变为10101010,通过修改不同的内容,即可修改SPI中0和1的持续时间。比如0xF0即为前半周期为高电平,后半周期为低电平的状态。在SPI的通信模式中,CPHA配置会影响该实验,下图展示了不同采样位置的SPI时序图[1]。CPOL = 0,CPHA = 1:CLK空闲状态 = 低电平,数据在下降沿采样,并在上升沿移出CPOL = 0,CPHA = 0:CLK空闲状态 = 低电平,数据在上升沿采样,并在下降沿移出。_stm32g431cbu6

计算机网络-数据链路层_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输-程序员宅基地

文章浏览阅读1.2k次,点赞2次,收藏8次。数据链路层习题自测问题1.数据链路(即逻辑链路)与链路(即物理链路)有何区别?“电路接通了”与”数据链路接通了”的区别何在?2.数据链路层中的链路控制包括哪些功能?试讨论数据链路层做成可靠的链路层有哪些优点和缺点。3.网络适配器的作用是什么?网络适配器工作在哪一层?4.数据链路层的三个基本问题(帧定界、透明传输和差错检测)为什么都必须加以解决?5.如果在数据链路层不进行帧定界,会发生什么问题?6.PPP协议的主要特点是什么?为什么PPP不使用帧的编号?PPP适用于什么情况?为什么PPP协议不_接收方收到链路层数据后,使用crc检验后,余数为0,说明链路层的传输时可靠传输

软件测试工程师移民加拿大_无证移民,未受过软件工程师的教育(第1部分)-程序员宅基地

文章浏览阅读587次。软件测试工程师移民加拿大 无证移民,未受过软件工程师的教育(第1部分) (Undocumented Immigrant With No Education to Software Engineer(Part 1))Before I start, I want you to please bear with me on the way I write, I have very little gen...

随便推点

Thinkpad X250 secure boot failed 启动失败问题解决_安装完系统提示secureboot failure-程序员宅基地

文章浏览阅读304次。Thinkpad X250笔记本电脑,装的是FreeBSD,进入BIOS修改虚拟化配置(其后可能是误设置了安全开机),保存退出后系统无法启动,显示:secure boot failed ,把自己惊出一身冷汗,因为这台笔记本刚好还没开始做备份.....根据错误提示,到bios里面去找相关配置,在Security里面找到了Secure Boot选项,发现果然被设置为Enabled,将其修改为Disabled ,再开机,终于正常启动了。_安装完系统提示secureboot failure

C++如何做字符串分割(5种方法)_c++ 字符串分割-程序员宅基地

文章浏览阅读10w+次,点赞93次,收藏352次。1、用strtok函数进行字符串分割原型: char *strtok(char *str, const char *delim);功能:分解字符串为一组字符串。参数说明:str为要分解的字符串,delim为分隔符字符串。返回值:从str开头开始的一个个被分割的串。当没有被分割的串时则返回NULL。其它:strtok函数线程不安全,可以使用strtok_r替代。示例://借助strtok实现split#include <string.h>#include <stdio.h&_c++ 字符串分割

2013第四届蓝桥杯 C/C++本科A组 真题答案解析_2013年第四届c a组蓝桥杯省赛真题解答-程序员宅基地

文章浏览阅读2.3k次。1 .高斯日记 大数学家高斯有个好习惯:无论如何都要记日记。他的日记有个与众不同的地方,他从不注明年月日,而是用一个整数代替,比如:4210后来人们知道,那个整数就是日期,它表示那一天是高斯出生后的第几天。这或许也是个好习惯,它时时刻刻提醒着主人:日子又过去一天,还有多少时光可以用于浪费呢?高斯出生于:1777年4月30日。在高斯发现的一个重要定理的日记_2013年第四届c a组蓝桥杯省赛真题解答

基于供需算法优化的核极限学习机(KELM)分类算法-程序员宅基地

文章浏览阅读851次,点赞17次,收藏22次。摘要:本文利用供需算法对核极限学习机(KELM)进行优化,并用于分类。

metasploitable2渗透测试_metasploitable2怎么进入-程序员宅基地

文章浏览阅读1.1k次。一、系统弱密码登录1、在kali上执行命令行telnet 192.168.26.1292、Login和password都输入msfadmin3、登录成功,进入系统4、测试如下:二、MySQL弱密码登录:1、在kali上执行mysql –h 192.168.26.129 –u root2、登录成功,进入MySQL系统3、测试效果:三、PostgreSQL弱密码登录1、在Kali上执行psql -h 192.168.26.129 –U post..._metasploitable2怎么进入

Python学习之路:从入门到精通的指南_python人工智能开发从入门到精通pdf-程序员宅基地

文章浏览阅读257次。本文将为初学者提供Python学习的详细指南,从Python的历史、基础语法和数据类型到面向对象编程、模块和库的使用。通过本文,您将能够掌握Python编程的核心概念,为今后的编程学习和实践打下坚实基础。_python人工智能开发从入门到精通pdf