FPGA-LCD基础驱动_fpga lcd cnt-程序员宅基地

技术标签: # FPGA学习篇

LCD的接口时序波形如图所示。VSYNC是场同步信号,低电平有效,从时序图可以看出,VSYNC是每一场(即也可以理解为每送一幅完整图像)的同步信号;与此类似,HSYNC是行同步信号,也是在每一行数据传输的开始产生几个时钟周期的低脉冲。这两个信号用于同步当前的数据信号,根据固定的脉冲约定,我们在某些时钟上升沿前将图像数据送到数据总线上供LCD内部锁存。

LCD驱动时序波形

这是LCD时序图中对应的时间参数。

表8.11 LCD驱动时序参数表

| 信号 |

列项 |

标记 |

最小值 |

标准值 |

最大值 |

单位 |

| Dclk |

频率 |

Tosc |

156 |

ns |

||

| 最大时间 |

Tch |

78 |

ns |

|||

| 最小时间 |

Tcl |

78 |

ns |

|||

| Data |

建立时间 |

Tsu |

12 |

ns |

||

| 保持时间 |

Thd |

12 |

ns |

|||

| Hsync |

周期 |

TH |

408 |

Tosc |

||

| 脉冲宽度 |

THS |

5 |

30 |

Tosc |

||

| 后沿 |

THB |

38 |

Tosc |

|||

| 显示周期 |

TEP |

320 |

Tosc |

|||

| 同步周期 |

THE |

36 |

68 |

88 |

Tosc |

|

| 前沿 |

THF |

20 |

Tosc |

|||

| Vsync |

周期 |

TV |

262 |

TH |

||

| 脉冲宽度 |

TVS |

1 |

3 |

5 |

TH |

|

| 后沿 |

TVB |

15 |

TH |

|||

| 显示周期 |

TVD |

240 |

TH |

|||

| 前沿 |

TVF |

2 |

4 |

TH |

相同的方式驱动的程序写法类似:

顶层文件:

module top(ext_clk_25m,ext_rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input ext_clk_25m;

input ext_rst_n;

output lcd_light_en;

output lcd_clk;

output lcd_hsy;

output lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

lcd_controller uut_lcd_controller(

.clk(ext_clk_25m),

.rst_n(ext_rst_n),

.lcd_light_en(lcd_light_en),

.lcd_clk(lcd_clk),

.lcd_hsy(lcd_hsy),

.lcd_vsy(lcd_vsy),

.lcd_r(lcd_r),

.lcd_g(lcd_g),

.lcd_b(lcd_b)

);

endmodule

lcd_controller.v

module lcd_controller(clk,rst_n,lcd_light_en,lcd_clk,lcd_hsy,lcd_vsy,lcd_r,lcd_g,lcd_b

);

input clk;

input rst_n;

output lcd_light_en;

output lcd_clk;

output reg lcd_hsy;

output reg lcd_vsy;

output [4:0] lcd_r;

output [5:0] lcd_g;

output [4:0] lcd_b;

parameter HSY_TH=9'D408-1'D1;//周期

parameter HSY_THS=9'D30 ;//脉冲宽度

parameter HSY_THB=9'D38 ;//后沿

parameter HSY_TEP=9'D320 ;//显示周期

parameter HSY_THE=9'D68 ;//同步周期

parameter HSY_THF=9'D20 ;//前沿

parameter VSY_TV=9'D262-1'D1;//周期

parameter VSY_TVS=9'D3 ;//脉冲宽度

parameter VSY_TVB=9'D15 ;//后沿

parameter VSY_TVD=9'D240 ;//显示周期

parameter VSY_TVF=9'D4 ;//前沿

//lcd背光常开

assign lcd_light_en=1'b1;

//配置驱动时钟6.25mHz

reg [1:0] lcd_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_cnt<=1'b0;

end

else begin

lcd_cnt<=lcd_cnt+1'b1;

end

end

assign lcd_clk=lcd_cnt[1];

wire dchange ={lcd_cnt==2'd2};

//X和Y轴计数器

reg[8:0] xcnt;

reg[8:0] ycnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

xcnt<=1'b0;

end

else if(dchange==1'b1)begin

if(xcnt==HSY_TH)begin

xcnt<=1'b0;

end

else begin

xcnt<=xcnt+1'b1;

end

end

else;

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

ycnt<=1'b0;

end

else if(dchange&&xcnt==HSY_TH)begin

if(ycnt==VSY_TV)begin

ycnt<=1'b0;

end

else begin

ycnt<=ycnt+1'b1;

end

end

else begin

ycnt<=ycnt;

end

end

//lcd显示的有效区域

reg valid;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

valid<=1'b0;

end

else if(ycnt>=(VSY_TVS+VSY_TVB)&&ycnt<(VSY_TVS+VSY_TVB+VSY_TVD)&&

xcnt>=(HSY_THS+HSY_THB)&&xcnt<(HSY_TEP+HSY_THB+HSY_THE))begin

valid<=1'b1;

end

else begin

valid<=1'b0;

end

end

//LCD驱动行场同步信号产生逻辑

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_hsy<=1'b1;

end

else if(xcnt==1'b0)begin

lcd_hsy<=1'b0;

end

else if(xcnt>=HSY_THS)begin

lcd_hsy<=1'b1;

end

else begin

lcd_hsy<=lcd_hsy;

end

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_vsy<=1'b1;

end

else if(ycnt==1'b0)begin

lcd_vsy<=1'b0;

end

else if(ycnt>=VSY_TVS)begin

lcd_vsy<=1'b1;

end

else begin

lcd_vsy<=lcd_vsy;

end

end

//产生显示条纹

reg [3:0]tmp_cnt;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid==1'b0)begin

tmp_cnt<=1'b0;

end

else if(valid&&dchange)begin

if(tmp_cnt<4'd9)begin

tmp_cnt<=tmp_cnt+1'b1;

end

else begin

tmp_cnt<=1'b0;

end

end

end

reg [15:0]lcd_db_rgb;

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

lcd_db_rgb<=16'd0;

end

else if(valid)begin

if((tmp_cnt==4'd9)&&dchange)begin

lcd_db_rgb[15:11]<=lcd_db_rgb[15:11]+1'b1;

end

else;

end

else begin

lcd_db_rgb<=1'b0;

end

end

assign lcd_r =valid ? lcd_db_rgb[15:11]:5'd0;

assign lcd_g =valid ? lcd_db_rgb[10:5]:6'd0;

assign lcd_b =valid ? lcd_db_rgb[4:0]:5'd0;

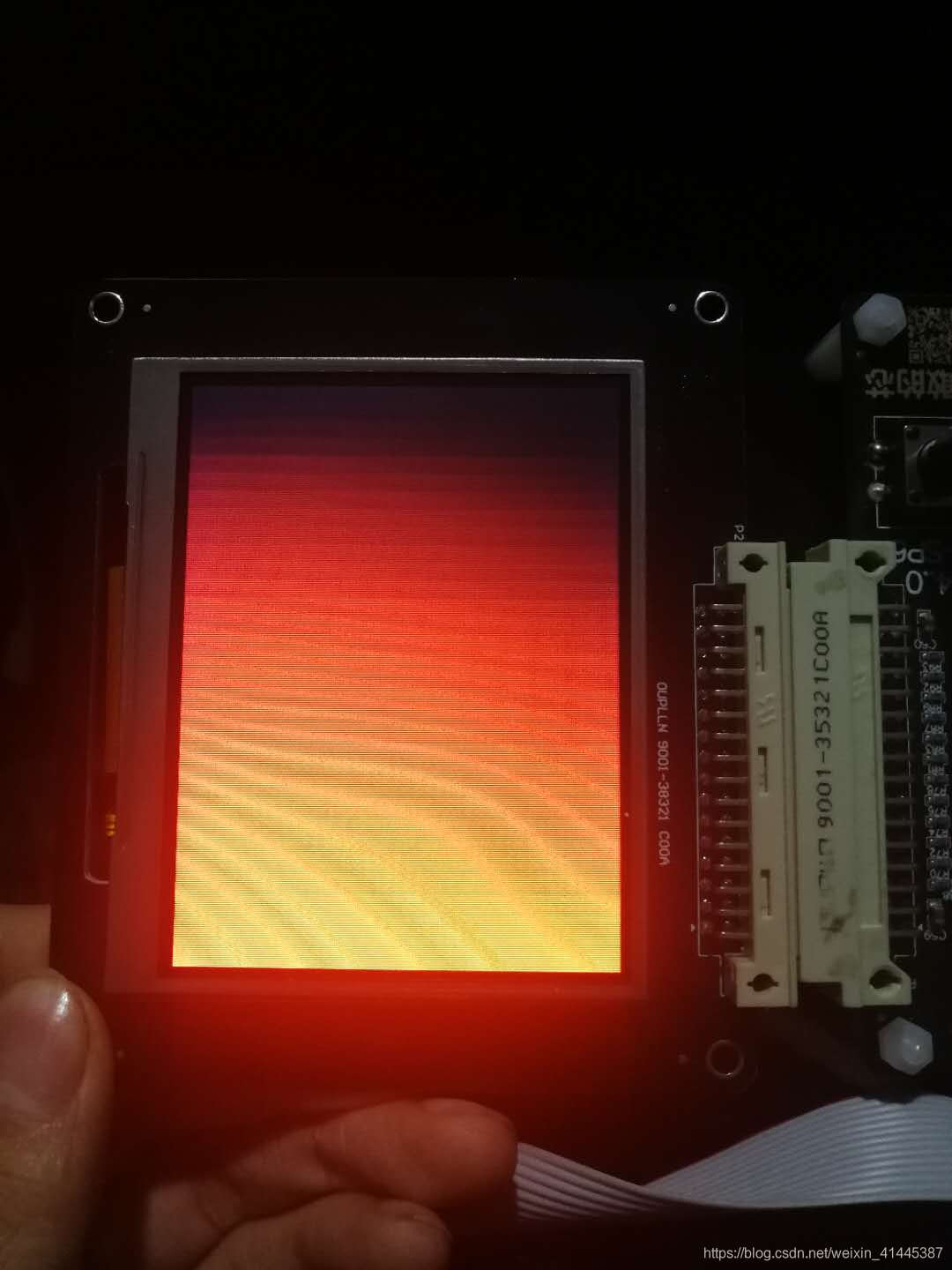

endmodule下板子效果图:

智能推荐

[architecture]-ARMV8的一些总结-一篇就够了_arm v8架构参考手册-程序员宅基地

文章浏览阅读8.4k次,点赞5次,收藏62次。ARM、armv8、armv9、arm架构、arm视频、添加vx : arm_2023 获取更多资料, arm资料、arm下载、arm学习、arm免费、arm课程,PE - processing elementARM体系结构定义了抽象机器的行为,称为处理元素(processing element),通常缩写为PE。与ARM体系结构兼容的实现必须符合处理元素所描述的行为。RISC架构ARM架构是一个精简指令集计算机(RISC)架构,具有以下RISC架构特征:- 一个大的统一寄存器文件。- 一种_arm v8架构参考手册

多维时序 | MATLAB实现RIME-CNN-LSTM-Multihead-Attention多头注意力机制多变量时间序列预测_matlab 概率稀疏自注意力-程序员宅基地

文章浏览阅读1.1k次,点赞20次,收藏17次。多维时序 | MATLAB实现RIME-CNN-LSTM-Multihead-Attention多头注意力机制多变量时间序列预测_matlab 概率稀疏自注意力

计算机和外部通信方式,计算机和外部的通信方式-程序员宅基地

文章浏览阅读2.9k次。计算机和外部交换信息又称为通信(Communication)。按数据传送方式分为并行通信和串行通信两种基本方式。1、并行通信并行通信就是把传送数据的n位数用n条传输线同时传送。其优点是传送速度快、信息率高。并且,通常只要提供二条控制和状态线,就能完成CPU和接口及设备之间的协调、应答,实现异步传输。它是计算机系统和计算机控制系统中常常采用的通信方式。但是并行通信所需的传输线(通常为电缆线)多,增加..._分别写出计算机移动终端连接外围设备的主要方式

ThinkPHP5框架知识付费系统uniapp+mysql可以部署PC+app+公众号+小程序版本-程序员宅基地

文章浏览阅读216次。ThinkPHP5框架知识付费系统uniapp+mysql可以部署PC+app+公众号+小程序版本。导师入住,添加课程和商品,出售后分红提现。vip svip功能。

电源管理(PMIC)TPS63070RNMR、TPS650942A0RSKR、LM5175RHFR器件介绍、应用及特点。-程序员宅基地

文章浏览阅读805次。电源管理(PMIC)TPS63070RNMR、TPS650942A0RSKR、LM5175RHFR器件介绍、应用及特点。_tps63070

Flask 通过Axios库前后端交互_flask 框架下axios-程序员宅基地

文章浏览阅读4.9k次。Axios 是一个基于promise的HTTP库,该库是一个更好的替代ajax向后端发送数据或请求数据的前端组件库,其本质上也是对原生XHR的封装,只不过它是Promise的实现版本,符合最新的ES规范,如下案例运用axios向后端提交JSON字符串,后端通过Flask响应请求并处理。Python后端使用Flask接收并处理前端发送过来的JSON字符串。前端发送数据的第一种方式。前端发送数据的第二种方式。_flask 框架下axios

随便推点

RHEL 5.1 安装Marvell Yukon网卡驱动_yk51驱动-程序员宅基地

文章浏览阅读1k次。linux下安装Marvell Yukon网卡驱动【提要】 我的主板是华硕P4P800 SE,集成Marvell Yukon网卡,安装redhat linux9后无法识别网卡,故需要费一点折腾了。。最终解决了linux中上网的问题,但引发了windows中无法连接的麻烦,暂时搁着先了。。。(2006-11-25回头圆满解决!)【内容】问题一开始就存在,我就一般在windows系统中寻找资料,下载资源,然后转到linux中,加载windows分区,获取文件。经过一段时间后,终于还是认真解决它好了。在windo_yk51驱动

Windows系统鼠标右键菜单添加打开cmd终端_we右键进入cmd-程序员宅基地

文章浏览阅读1.4k次,点赞3次,收藏2次。直接拷贝上面的一段代码,保存到文本文档,然后把.txt后缀改为.reg,然后右键该文件,点击合并即可。这样,鼠标右键菜单就有open cmd here即在当前路径打开cmd这个选项了,但是这个是普通用户运行cmd。有时候,当要在某个文件夹下打开cmd终端时,如果没有右键菜单快捷方式,就得打开cmd后,使用cd方式进入 当前目录,很麻烦。同时还会添加另一个选项,以管理员身份运行(A) ,这个是以管理员身份运行cmd。文件名:右键在此处运行cmd.reg。以下的脚本,可以帮你解决这个问题。_we右键进入cmd

python汇编语言还是机器语言_深入理解计算机系统(3.1)------汇编语言和机器语言...-程序员宅基地

文章浏览阅读136次。《深入理解计算机系统》第三章——程序的机器级表示。作者首先讲解了汇编代码和机器代码的关系,阐述了汇编承上启下的作用;接着从机器语言IA32着手,分别讲述了如何存储数据、如何访问数据、如何完成运算以及如何进行跳转。通过这些步骤,又告诉了我们分支语句、循环语句是怎么完成的,函数调用、栈帧结构以及递归过程。最后能通过编译器产生的汇编代码表示,我们要了解编译器和它的优化能力,知道编译器能为我们完成哪些工作..._phthon 汇编语言 机器语言

android毕设各种app项目,安卓毕设,android毕设_app毕业设计-程序员宅基地

文章浏览阅读3w次,点赞44次,收藏271次。闲来无事,整理了一些对之前帮同学做过的小项目,希望能 帮到正在紧张准备毕设项目的你!项目挺多总有一个适合你! 如果有问题需要帮忙 我也可以帮忙指导指导。说明: 以下项目均使用Android studio开发,代码使用java语言,布局文件使用xml,后端接口部署在自己的阿里云上面类似京东商城app首先是登录、注册,然后进入首页使用viewpager+fragment实现四个不同tab的切换,tab包括(商品列表、促销商品、购物车、我的) @Override protected vo_app毕业设计

Keil侧边工具栏(项目窗口)打开方式_keil侧边栏-程序员宅基地

文章浏览阅读3.2k次,点赞10次,收藏4次。不废话解决问题_keil侧边栏

算法学习,转载记录(持续记录)-程序员宅基地

文章浏览阅读54次。个人转载记录算法优质文章,仅做笔记,侵删