【转】MBIST总结-程序员宅基地

随着半导体工艺尺寸不断缩小,IC设计的规模越来越大,高度复杂的IC产品正面临着高可靠性、高质量、低成本以及更短的产品上市周期等日益严峻的挑战。一方面随着半导体工艺尺寸的缩小,嵌入式存储器可能存在的缺陷类型越来越多;另一方面,随着IC产品的复杂度的提高,ROM、RAM、EEPROM在IC产品中的比重越来越大。

嵌入式存储器的可测试设计技术包括直接测试、用嵌入式cpu进行测试和内建自测试技术(MBIST)。直接测试方法利用自动测试设备进行测试,可以轻易实现多种高质量测试算法,但是这种方法存在着一些不足之处,一是在ATE机上实现的算法越复杂,对ATE机存储器的容量要求越高,测试的费用也就越高;二是在ATE机上不易实现对嵌入式存储器的“全速”测试,测试时钟的工作频率越高,测试成本越高;三是由于芯片外围管脚的限制,对芯片内大容量嵌入式存储器进行直接测试往往不大现实。利用嵌入式CPU进行测试的好处在于不需要对设计硬件做任何修改,而且测试算法的修改与实现可以通过灵活修改CPU软件程序完成。但是这种方法也存在缺点,首先是设计中的CPU并没有和所有的嵌入式存储器直接相连,其次编写或修改软件程序实现测试算法需要耗费大量的人力,另外这种方法还很难对存储CPU程序的存储器进行测试。

MBIST技术的缺点是增加了芯片的面积并有可能影响芯片的时序特性,然而,随着存储器容量的增加,这种方法所增加的芯片面积所占的比例相对很小,而且这种测试技术还有很多其它技术优势。首先它可以实现可测性设计的自动化,自动实现通用存储器测试算法,达到高测试质量、低测试成本的目的;其次MBIST电路可以利用系统时钟进行“全速”测试,从而覆盖更多生成缺陷,减少测试时间;最后它可以针对每一个存储单元提供自诊断和自修复功能。此外MBIST的初始化测试向量可以在很低成本的测试设备上进行。所以,从高测试质量、低测试成本的角度考虑,MBIST是目前嵌入式存储器测试设计的主流技术。

MBIST概述

BIST是一种结构性DFT技术,它将器件的测试结构置于该器件内部。BIST结构可以测试多种类型的电路,包括随机逻辑器件和规整的电路结构如数据通道、存储器等。BIST电路视其应用对象不同其实现存在显著差异,但任何类型的BIST都有共同的用途。BIST结构可以针对目标电路自动生成各种测试向量,并对输出响应进行比较。目标电路的类型也呈现多样化特征,它可以是整个芯片设计,也可以是设计模块或设计模块中的某个结构。此外,测试向量生成以及输出比较电路也可能存在差异。

下面我们主要探讨MBIST。大型、复杂电路通常包含多处难以测试的逻辑部分,即使就可测试性最好的大型设计而言,也同样需要耗费大量测试生成时间、占用大量的ATE存储器和ATE测试时间,所有这些都是非常昂贵,但对于采用ATPG方法进行测试而言又是必需的。另外,由于存储器缺陷类型不同于一般逻辑的缺陷类型,存储器在较大规模设计之中层次较深,ATPG通常不能提供完备的存储器测试解决方案,而MBIST技术则可以解决这些问题。BIST能够在不牺牲检测质量的前提下提供一种存储器测试解决方案,在很多情况下,BIST结构可以彻底消除或最大限度减少对外部测试向量生成(以及ATE机存储器容量)和测试应用时间的需要。设计人员可以在某设计内部执行MBIST电路,并由于MBIST电路邻近被测试的存储器而轻易实现全速测试,设计人员也可以从该设计的较高层次运行MBIST流程。

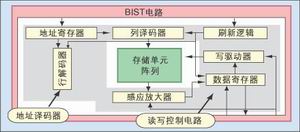

MBIST电路以某项设计中的RAM和ROM模型为目标。前面已经提到,由于存储器缺陷类型不同于一般逻辑的缺陷类型,所以检测RAM和ROM不同于检测随机逻辑,MBIST针对检测RAM和ROM共有的缺陷类型采用了有效的电路和算法。MBIST电路还可以基于各种算法生成多种测试向量,每种测试向量都着重测试一种特定的电路类型或错误类型。比较电路具有多种独特的实现方式,其中包括比较器和标签分析器。存储器电路模型一般由三个基本模块组成,分别是地址译码器、读/写控制逻辑以及存储单元阵列(图1)。

图 1

MBIST架构

MBIST通常采用一种或多种算法为测试存储器一种或多种缺陷类型而特别设计,MBIST电路包括测试向量产生电路、BIST控制电路、响应分析器三部分(图2)。

图 2

测试向量产生电路可生成多种测试向量,不同的测试算法实现的电路所产生的测试向量内容也不同;BIST控制电路通常由状态机实现,控制BIST对存储器的读写操作,响应分析器既可以用比较器实现,也可以用压缩器多输入移位寄存器(MISR)电路实现,它对照已知正常的存储器响应,比较实际存储器模型响应并检测器件错误。

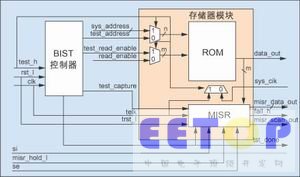

采用比较器实现的MBIST电路如图3所示,该电路提供两个标志输出信号tst_done和fail_h通知系统测试进程的状态和结果。tst_done在测试结束时被置为有效状态,在测试过程中发现任何错误,fail_h信号即置为有效并保持到测试结束。采用压缩器实现的MBIST电路如图4所示,该电路提供了基于MISR的比较技术,测试结束后可以输出压缩后的标签寄存器结果。

图 3 比较器实现的MBIST电路

图 4 压缩器实现的MBIST电路

通常情况下,MBIST电路不仅可以筛选出失效的器件,还能够自动分析失效的原因,此时测试数据同时被用来分析定位存储器失效的具体地址空间。

此外,特殊的MBIST电路还可以提供自诊断和自修复功能。在MBIST电路中引入内建自分析模块,BIST模块根据失效的数据和地址等信息输出相应的控制信号R2R1R0,把系统对存储器失效地址空间的读写操作指向用于自修复冗余设计。

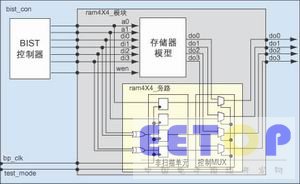

MBIST电路通常还包括BIST Collar模块,BIST Collar模块的内容包括流水处理电路、扫描旁路电路、多路复用器电路和MISR电路等,其中扫描旁路电路最为常用(图5)。

图 5 带扫描旁路电路的MBIST

MBIST实现与EDA工具

MBIST工具允许设计人员将更多时间花在设计工作中,而不是在有关测试的问题上忧心忡忡。工具已经内建了开发存储器测试和管理BIST电路所必需的知识,其生成的故障诊断电路允许设计人员对故障数据进行识别和分析。它可以产生相应的testbench,方便对MBIST外围电路逻辑开展验证,还可产生相应的自动化脚本文件以有助于逻辑综合的自动化运行。此外对任何EDA工具来说,要想有效工作就必须能够适应设计者现有的设计流程,遵循各种行业标准。

MBISTArchitect是Mentor公司提供的MBIST自动化EDA工具。它可以针对一个或多个嵌入式存储器开发嵌入式测试电路,自动实现存储器单元或阵列的RTL级内建自测试电路。它支持多种测试算法,可对一个或多个内嵌存储器自动创建BIST逻辑,并完成BIST逻辑与存储器的连接,另外还能在多个存储器之间共享BIST控制器,实现并行测试,从而缩短测试时间并节约芯片面积。MBIST结构中还可以包括故障的自动诊断功能,方便了故障定位和开发针对性的测试向量。

http://bb2hh.blogbus.com/logs/74731326.html

1. ROM bist

ROM由于只能读,所以不能任意的输入特定的测试向量,但是通过读出ROM内容,逐个地址比较的方法对于大容量的ROM非常的浪费时间,于是有人提供了一种算法,即读出一个地址,该地址的内容做校验(CRC?),校验值参与下一个地址的校验,扫描所有的地址之后得到一个最终的校验值,将这个值通过scan port shift出来进行比较。也可以内部比较这个值,输出fail/pass结果。请看这个例子。

model DROM (Q, CLK, CEN, A)

bist_definition (

address A(array=11:0;);

data_out Q(array=63:0;);

clock CLK high;

output_enable CEN low;

vendor = arm;

version = "1.0";

message = "synchronous 4096X64 ROM";

min_address = 0;

max_address = 4095;

data_size = 64;

read_cycle (

change A;

assert CEN;

wait;

wait;

expect Q move;

)

)

)

)

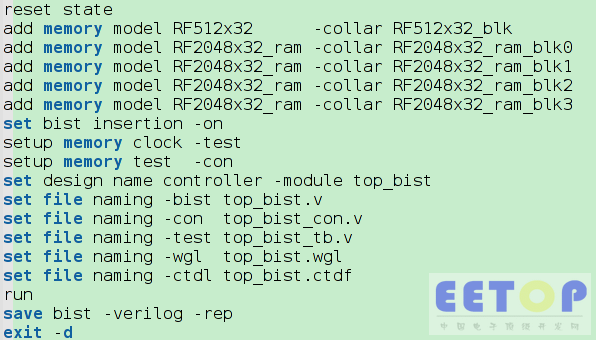

// rom_bist.do

reset state

load lib ../bist_model/DROM.vm

add memory model DROM_B3

add memory model IROM_B1

add memory model IROM_B1_MR

add memory model IROM_B2

add memory model IROM_B3

setup mbist algorithms Rom2

set design name controller -module SPROM_4096X64_bist

set file naming -bist_model ../result/SPROM_4096X64_bist.v

set file naming -connected_model ../result/SPROM_4096X64_bist_con.v

set file naming -testbench ../result/SPROM_4096X64_bist_tb.v

set file naming -script. ../result/SPROM_4096X64_bist.v_dcscript

set file naming -ctdl ../result/SPROM_4096X64_bist.v_ctdf

set file naming -wgl ../result/SPROM_4096X64_bist.v_wgl

run

save bist -verilog -script. -replace

exit –discard

mbistarchitect \

SRAM是一种单口的静态RAM,可以读写,所以我们可以控制往RAM中写入的内容,然后读出来比较。这类bist算法很多,常用March2算法,可以检查address decoder faults (AF), stuck at faults(SAF), transition faults (TF), stuck open faults (SOF), inversion coupling faults (CFin), and linkedidempotent coupling faults (CFid)这些问题。

下面给出一个model的例子,运行脚本和ROM类似。

model SPRAM_512X32 (Q,CLK,CEN,WEN,A,D,OEN)

bist_definition (

address A(array=8:0;);

data_in D(array=31:0;);

data_out Q(array=31:0;);

clock CLK high;

chip_enable CEN low;

write_enable WEN low;

dont_touch OEN high;

vendor = ARM;

version = "1.0";

message = "synchronous 512X32 RAM";

min_address = 0;

max_address = 511;

data_size = 32;

write_cycle (

change A;

change D;

assert CEN;

assert WEN;

wait;

)

change A;

assert CEN;

wait;

wait;

expect Q move;

)

)

)

)

DRAM是双口的RAM,一般有两种类型,第一种是两套接口都可以完成读写操作,第二种是一套口专门读,另一套口专门写,所用的bist算法与SRAM相同。下面给出一个例子。

model DPRF_128X32 (QA,AA,CLKA,CENA,AB,DB,CLKB,CENB)

bist_definition (

address AA(array=6:0;);

address AB(array=6:0;);

data_in DB(array=31:0;);

data_out QA(array=31:0;);

clock CLKA high;

clock CLKB high;

read_enable CENA low;

write_enable CENB low;

vendor = ARM;

version = "1.0";

message = "synchronous 128X32 dual port RAM";

min_address = 0;

max_address = 127;

data_size = 32;

write_cycle (

change AB;

change DB;

assert CENB;

wait;

)

)

read_port (

read_cycle (

change AA;

assert CENA;

wait;

wait;

expect QA move;

)

)

)

)

总结:Mentor的工具在产生bist的时候比较强大,美中不足的是需要我们用它自己的语法来描述memory对象,不过好在其语法比较简单。所以model能不能写的符合要求,能不能与vendor提供的model一直十分的重要,也是要特别注意的地方。

- mbist:RTL或gate level插入,采用TMS或SMS。

- scan:gate level插入,采用dftc,很少公司用tessent。

- edt:gate level插入,采用tessent或testkompress。

- atpg:采用tessent或testkompress(业界一骑绝尘的atpg工具)

- formal:采用synopsys的fm。

- timing:采用synopsys的pt。

- dv(dft verification):采用vcs或irun。

mbist方面,小一点的公司一般会采用TMS,就是tessent mbist system,mentor的工具。大的公司,比如海思等,采用SMS,就是star memory system,synopsys的工具。

重点是scan方面,我比较了tessent和dftc工具。

| 工具 |

优点 |

缺点 |

| tessent |

1. 插scan十分快,时间短。 2. 直接生成供atpg的dofile和testproc文件 3. 通过比较,atpg覆盖率比dftc强。 |

需要配置scan工作环境 |

| dftc |

1. 可以直接使用DC的环境 2. 优化能力强(此处有疑问) |

1. 耗用大量时间,插scan时间极长。 2. 需要用脚本或人工生成供atpg的dofile和testpro文件。 2. 通过对比,覆盖率不可能强过tessent |

tessent

优点:

1. 插scan很快,节省时间,40多万个寄存器的电路,几分钟就插好scan。而且大部分时间是在check_design_rules。可能tessent只是把general register替换成scan regist,然后连接起来。

2. 直接生成供atpg的dofile和testproc文件,少不少麻烦,也避免许多drc问题。

3. 在同样scan情况下,感觉atpg的test coverage要高一些。

缺点:

需要配工作环境。

dftc

优点:

1. 使用DC的环境。

2. 据说是因为其优化能力强。可是插scan时,没添加过约束啊,何来优化?

缺点:

1. 插scan时,极耗时。40多万个寄存器的电路,要半个小时,大部分时间在map。

2. 需要用脚本或者人工生成供atpg的dofile和testproc文件。

3. 做atpg时,会碰到大量drc问题,尤其不好解决的D1 violation,就是那种报disturb的现象。

4. 通过对比,覆盖率强不过用tessent插的scan。

在插scan时,tessent和dftc工具,对方功能两者互有。个人比较喜欢使用tessent插scan,省事。

另外,感觉用一家公司工具的覆盖率都要高,dftc+tmax的atpg覆盖率,也比混合流程要高。

大家做edt时,考虑过压缩比了吗?内部扫描链设多长?dftc也有compress结构,我没做过对比,我觉得肯定不好。

但好多公司用dftc插scan,就连mentor都推荐这种混合方案。

欢迎大家留言,或者本人有说的不全不对的地方,望大家补充。给个面子,说说各位同行用什么插scan的,大家共同进步。

智能推荐

c# 调用c++ lib静态库_c#调用lib-程序员宅基地

文章浏览阅读2w次,点赞7次,收藏51次。四个步骤1.创建C++ Win32项目动态库dll 2.在Win32项目动态库中添加 外部依赖项 lib头文件和lib库3.导出C接口4.c#调用c++动态库开始你的表演...①创建一个空白的解决方案,在解决方案中添加 Visual C++ , Win32 项目空白解决方案的创建:添加Visual C++ , Win32 项目这......_c#调用lib

deepin/ubuntu安装苹方字体-程序员宅基地

文章浏览阅读4.6k次。苹方字体是苹果系统上的黑体,挺好看的。注重颜值的网站都会使用,例如知乎:font-family: -apple-system, BlinkMacSystemFont, Helvetica Neue, PingFang SC, Microsoft YaHei, Source Han Sans SC, Noto Sans CJK SC, W..._ubuntu pingfang

html表单常见操作汇总_html表单的处理程序有那些-程序员宅基地

文章浏览阅读159次。表单表单概述表单标签表单域按钮控件demo表单标签表单标签基本语法结构<form action="处理数据程序的url地址“ method=”get|post“ name="表单名称”></form><!--action,当提交表单时,向何处发送表单中的数据,地址可以是相对地址也可以是绝对地址--><!--method将表单中的数据传送给服务器处理,get方式直接显示在url地址中,数据可以被缓存,且长度有限制;而post方式数据隐藏传输,_html表单的处理程序有那些

PHP设置谷歌验证器(Google Authenticator)实现操作二步验证_php otp 验证器-程序员宅基地

文章浏览阅读1.2k次。使用说明:开启Google的登陆二步验证(即Google Authenticator服务)后用户登陆时需要输入额外由手机客户端生成的一次性密码。实现Google Authenticator功能需要服务器端和客户端的支持。服务器端负责密钥的生成、验证一次性密码是否正确。客户端记录密钥后生成一次性密码。下载谷歌验证类库文件放到项目合适位置(我这边放在项目Vender下面)https://github.com/PHPGangsta/GoogleAuthenticatorPHP代码示例://引入谷_php otp 验证器

【Python】matplotlib.plot画图横坐标混乱及间隔处理_matplotlib更改横轴间距-程序员宅基地

文章浏览阅读4.3k次,点赞5次,收藏11次。matplotlib.plot画图横坐标混乱及间隔处理_matplotlib更改横轴间距

docker — 容器存储_docker 保存容器-程序员宅基地

文章浏览阅读2.2k次。①Storage driver 处理各镜像层及容器层的处理细节,实现了多层数据的堆叠,为用户 提供了多层数据合并后的统一视图②所有 Storage driver 都使用可堆叠图像层和写时复制(CoW)策略③docker info 命令可查看当系统上的 storage driver主要用于测试目的,不建议用于生成环境。_docker 保存容器

随便推点

网络拓扑结构_网络拓扑csdn-程序员宅基地

文章浏览阅读834次,点赞27次,收藏13次。网络拓扑结构是指计算机网络中各组件(如计算机、服务器、打印机、路由器、交换机等设备)及其连接线路在物理布局或逻辑构型上的排列形式。这种布局不仅描述了设备间的实际物理连接方式,也决定了数据在网络中流动的路径和方式。不同的网络拓扑结构影响着网络的性能、可靠性、可扩展性及管理维护的难易程度。_网络拓扑csdn

JS重写Date函数,兼容IOS系统_date.prototype 将所有 ios-程序员宅基地

文章浏览阅读1.8k次,点赞5次,收藏8次。IOS系统Date的坑要创建一个指定时间的new Date对象时,通常的做法是:new Date("2020-09-21 11:11:00")这行代码在 PC 端和安卓端都是正常的,而在 iOS 端则会提示 Invalid Date 无效日期。在IOS年月日中间的横岗许换成斜杠,也就是new Date("2020/09/21 11:11:00")通常为了兼容IOS的这个坑,需要做一些额外的特殊处理,笔者在开发的时候经常会忘了兼容IOS系统。所以就想试着重写Date函数,一劳永逸,避免每次ne_date.prototype 将所有 ios

如何将EXCEL表导入plsql数据库中-程序员宅基地

文章浏览阅读5.3k次。方法一:用PLSQL Developer工具。 1 在PLSQL Developer的sql window里输入select * from test for update; 2 按F8执行 3 打开锁, 再按一下加号. 鼠标点到第一列的列头,使全列成选中状态,然后粘贴,最后commit提交即可。(前提..._excel导入pl/sql

Git常用命令速查手册-程序员宅基地

文章浏览阅读83次。Git常用命令速查手册1、初始化仓库git init2、将文件添加到仓库git add 文件名 # 将工作区的某个文件添加到暂存区 git add -u # 添加所有被tracked文件中被修改或删除的文件信息到暂存区,不处理untracked的文件git add -A # 添加所有被tracked文件中被修改或删除的文件信息到暂存区,包括untracked的文件...

分享119个ASP.NET源码总有一个是你想要的_千博二手车源码v2023 build 1120-程序员宅基地

文章浏览阅读202次。分享119个ASP.NET源码总有一个是你想要的_千博二手车源码v2023 build 1120

【C++缺省函数】 空类默认产生的6个类成员函数_空类默认产生哪些类成员函数-程序员宅基地

文章浏览阅读1.8k次。版权声明:转载请注明出处 http://blog.csdn.net/irean_lau。目录(?)[+]1、缺省构造函数。2、缺省拷贝构造函数。3、 缺省析构函数。4、缺省赋值运算符。5、缺省取址运算符。6、 缺省取址运算符 const。[cpp] view plain copy_空类默认产生哪些类成员函数