”时序分析“ 的搜索结果

fpga 静态时序分析 是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

XILINX 时序约束使用指南笔记 ——时序约束介绍 时序约束方法 时序约束原则等

53777 集成电路静态时序分析与建模。。。。。。。

但是到了高速时钟或者双沿采样或者发射沿和数据对齐的情况下,这时候就需要告诉VIVADO外部的时钟与数据情况来让VIVADO分析能否满足建立时间与保持时间。INPUT约束仅仅只是告诉VIVADO外部的时钟情况,而内部的布局...

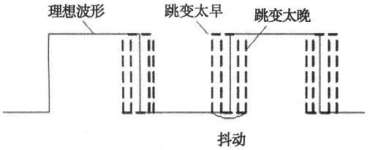

和PCB一样,FPGA内部的信号传递也需要时间,通过逻辑门也需要一定的延迟。这些延迟在低时钟频率下可以忽略不计,但是在高...为了防止出现时序违例,就需要对FPAG内部的延迟和走线进行分析。使数据和时钟更好的吻合。

时序分析主要有两种办法:静态时序分析: (static timing analysis,STA),是遍历电路存在的所有时序路径,根据给定工作条件(PVT)下的时序库.lib文件计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否...

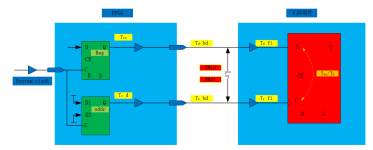

T1:时钟延迟(已知) T_cycle:时钟周期(已知) △T=T3-T2(已知)时钟偏斜 建立时间 :Ts=T_cycle-T1+△T 建立时间约束(Tsetup),建立时间余量Tslack=Ts-Tsetup 保持时间:Th=T1-△T或者Th=T_cycle-Th ...

在第一节里面有保持时间的定义,也就是采样沿到达后,数据应该保持的最小时间。

何谓静态时序分析(Static Timing Analysis,简称STA) 它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求...

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种很简单的解读办法,...

数字集成电路静态时序分析基础.pdf

在第一节里面有保持时间的定义,也就是采样沿到达后,数据应该保持的最小时间。

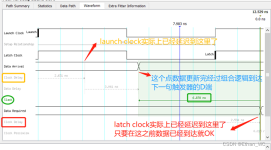

知道了建立时间在数字电路中的计算方式以及时序分析的基本概念之后,就需要在软件中来查看并优化我们的时序了,首先最重要的就是学会看时序分析报告。

非常有用的学习文件!非常非常有用!课程目录如下: 1.静态时序的概念、目的; 2.静态时序分析路径; 3.静态时序分析方法; 4.静态时序分析工具介绍; 5.静态时序分析报告及逻辑优化设计。

本文今天带大家学习一下 从静态时序分析到SDRAM时序收敛的时序。

FPGA中亚稳态【Tsu建立时间】【Th保持时间】【Tmet决断时间】【recovery恢复时间】【removal移除时间】CDC跨时钟域处理及相应的时序约束【set_clock_groups】【set_max_delay】

正点原子FPGA静态时序分析与时序约束_V1.0.pdf

我们先来看看时序分析器如何打开,单独运行版本,可以从ISE的程序启动目录下打开,如图1所示。 图1 启动单独运行时序分柝器 打开时序分析器后,需要指定NCD设计文件和PCF约束文件。如果要做Post-MAP(映射后)...

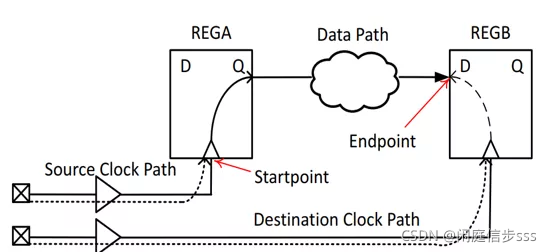

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。实际进行时序分析时,可不必每次都这么转换,但是不得不...

ARMA模型时间序列分析法简称为时序分析法,是一种利用参数模型对有序随机振动响应数据进行处理,从而进行模态参数识别的方法。参数模型包括AR自回归模型、MA滑动平均模型和ARMA自回归滑动平均模型

静态时序分析经典.pdf

标签: sta

时序分析的精典,适合新人学习。讲得很好,适合用来打基础。。。。。。。。。。。。。。。。。。。。。。。。。。。欢迎大家一起学习

4 时序约束与时序分析.pdf

标签: 时序约束

时序约束与时序分析

静态时序分析实践.rar

标签: STA

1小时玩转数字电路.rar AHB-SRAMC和FIFO的设计与验证.rar clock skew.rar IC攻城狮求职宝典.rar linux basic.rar Linux EDA虚拟机 - 个人学习IC设计.rar Perl语言在芯片设计中的应用.rar SoC芯片设计技能专题.rar ...

静态时序分析(SAT) 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及...

推荐文章

- 利用playbook安装和卸载nginx_playbook 卸载nginx-程序员宅基地

- Leetcode--有效的括号-程序员宅基地

- 使用expdp工具导出数据库下的scott用户的相关信息,不导出表数据,只想导出相关的元数据(表和索引相关定义)-程序员宅基地

- 生成矩阵_生成经济距离空间权重矩阵的Stata代码-程序员宅基地

- oracle中如何创建/删除数据库的实例_oracle9i如何删除和创建实例-程序员宅基地

- java计算机毕业设计高校人事管理系统MyBatis+系统+LW文档+源码+调试部署-程序员宅基地

- Linux下实现蜜罐系统_硬件:局域网内联网的两台主机,其中一台linux操作系统主机安装“蜜罐”。另一台为w-程序员宅基地

- 洛谷 1073 最优贸易 NOIP2009T3 SPFA-程序员宅基地

- 【Centos 7】【Docker】 安装 kafka_centos kafka docker-程序员宅基地

- VulnHub-DRIFTINGBLUES: 3_nmap -sp ip/mask-程序员宅基地